# MIPS32® microAptiv<sup>™</sup> UP Processor Core Family Integrator's Guide

Document Number: MD00941 Revision 01.01 July 30, 2014

Imagination Technologies Ltd. 955 East Arques Avenue Sunnyvale, CA 94085-4521

**IMAGINATION TECHNOLOGIES PROPRIETARY / CONFIDENTIAL**

*Aptiv*<sup>™</sup>

<u>Confidential</u>. Neither the whole nor any part of this document/material, nor the product described herein, may be adapted or reproduced in any material form except with the written permission of Imagination. All logos, products and trade marks are the property of their respective owners. This document may only be distributed subject to the terms of an applicable Non-Disclosure or Licence Agreement with Imagination.

Template: nDb1.03, Built with tags: 1D

MIPS32® microAptiv™ UP Processor Core Family Integrator's Guide, Revision 01.01

**IMAGINATION TECHNOLOGIES PROPRIETARY / CONFIDENTIAL**

## **Table of Contents**

| Chapter 1: Overview                                                  | 9  |

|----------------------------------------------------------------------|----|

| 1.1: Environment Variable Setup                                      |    |

| 1.1.1: microAptiv UP Deliverables                                    |    |

| 1.2: Other Documents                                                 | 10 |

| Chapter 2: Signal Descriptions                                       |    |

| 2.1: Naming Conventions                                              |    |

| 2.2: Top-level Hierarchy                                             |    |

| 2.3: Detailed Signal Descriptions                                    |    |

| 2.3.1: Signals at m14k_cpu Level                                     |    |

| 2.3.2: External Interface Signals on m14k_top Level to Custom Blocks |    |

| Chapter 3: AHB-Lite Interface                                        |    |

| 3.1: Interface Transactions                                          |    |

| 3.1.1: Basic Transfers                                               |    |

| 3.1.2: Transfer Types                                                |    |

| 3.1.3: Transfer Size                                                 |    |

| 3.1.4: Burst Operation                                               |    |

| 3.1.5: Waited Transfers                                              |    |

| 3.1.6: Protection Control                                            |    |

| 3.1.7: Locked Transfers                                              |    |

| 3.2: Clock Ratios                                                    |    |

| 3.3: Write Buffer                                                    |    |

| 3.4: Merging Control                                                 |    |

| Chapter 4: Interrupt Interface                                       |    |

| 4.1: Introduction                                                    |    |

| 4.2: Compatibility and Vectored Interrupt Modes                      |    |

| 4.3: External Interrupt Controller Mode                              |    |

| Chapter 5: EJTAG Interface                                           |    |

| 5.1: EJTAG versus JTAG                                               |    |

| 5.1.1: EJTAG Similarities to JTAG                                    |    |

| 5.1.2: Sharing EJTAG Resources with JTAG                             |    |

| 5.2: How to Connect EJ_* Pins                                        |    |

| 5.2.1: EJTAG Chip-Level Pins                                         |    |

| 5.2.2: EJTAG Device ID Input Pins                                    |    |

| 5.2.3: EJTAG Software Reset Pins                                     |    |

| 5.3: cJTAG Interface                                                 |    |

| 5.4: Multi-Core Implementations                                      |    |

| 5.4.1: TDI/TDO Daisy-Chain Connection                                |    |

| 5.4.2: Multi-Core Breakpoint Unit                                    |    |

| 5.5: Trace Capability                                                |    |

| 5.6: SecureDebug                                                     |    |

| Chapter 6: Coprocessor Interface                                     |    |

| 6.1: Introduction                                                  |    |

|--------------------------------------------------------------------|----|

| 6.2: Coprocessor Instructions                                      |    |

| 6.3: Signal Configuration                                          |    |

| 6.4: Interface Protocols                                           |    |

| 6.4.1: Instruction Dispatch                                        |    |

| 6.4.2: To Coprocessor Data Transfer                                |    |

| 6.4.3: From Coprocessor Data Transfer                              |    |

| 6.4.4: Condition Code Checking                                     |    |

| 6.4.5: Coprocessor Exceptions                                      |    |

| 6.4.6: Instruction Nullification                                   |    |

| 6.4.7: Instruction Killing                                         |    |

| 6.5: Power Saving Issues                                           |    |

| 6.5.1: No Coprocessor Present                                      |    |

| 6.5.2: How to Use CP2_idle                                         |    |

| 6.5.3: Gating the Clock to the Coprocessor                         |    |

| 6.5.4: Using Strobe Signals as Gating Inputs on the Sub-interfaces |    |

| 6.6: Template for Coprocessor Modules                              |    |

|                                                                    |    |

| Oberster 7: Ceretebred DAM Interfere                               | 75 |

| Chapter 7: Scratchpad RAM Interface                                |    |

| 7.1: SPRAM Features                                                |    |

| 7.2: SPRAM Overview                                                |    |

| 7.2.1: SPRAM Differences From a Cache                              |    |

| 7.2.2: Independent Tag/Data Accesses                               |    |

| 7.2.3: Timing Considerations                                       |    |

| 7.2.4: Delayed Stores                                              |    |

| 7.2.5: Tag Reads and Writes                                        |    |

| 7.2.6: Backstalling the SPRAM Interface                            |    |

| 7.2.7: Access Granularity                                          |    |

| 7.2.8: Write Strobe with 0 Write Mask                              |    |

| 7.2.9: Unified I/D SPRAM                                           |    |

| 7.2.10: Restartability of SPRAM Accesses                           |    |

| 7.2.11: Connecting I/O Devices to the Scratchpad Interface         |    |

| 7.2.12: Null Connection to Unused SPRAM Interface                  |    |

| 7.3: SPRAM Interface Transactions                                  |    |

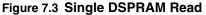

| 7.3.1: Single Read                                                 |    |

| 7.3.2: Single Multi-Cycle Read                                     |    |

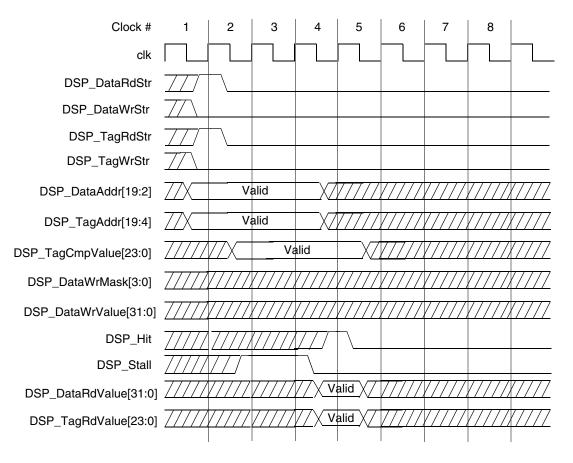

| 7.3.3: Single Write                                                |    |

| 7.3.4: Single Multi-Cycle Write                                    |    |

| 7.3.5: Simultaneous Tag Read and Data Write                        |    |

| 7.3.6: Back-to-Back Reads                                          |    |

| 7.3.7: Read-Write-Read Sequence                                    |    |

| 7.3.8: Read-Modified-Write Sequence (Locked transfers)             |    |

| 7.4: External Access to Scratchpad Memory                          |    |

| 7.5: SPRAM Initialization                                          |    |

| 7.6: Using the Same Design for ISPRAM and DSPRAM                   |    |

| 7.7: Multiple SPRAM Regions                                        |    |

| 7.8: Implementation Recommendations                                |    |

| 7.8.1: Software-visible Configuration Information                  |    |

| 7.8.2: Region Sizes                                                |    |

| 7.8.3: Unique Addresses                                            |    |

| 7.8.4: Support ISPRAM Writes                                       |    |

| 7.8.5: Virtual Aliasing                                            |    |

| 7.8.6: SPRAM Parity Support                                        |    |

| Chapter 8: Clocking, Reset, and Power                               |     |

|---------------------------------------------------------------------|-----|

| 8.1: Clocking                                                       |     |

| 8.1.1: SI_ClkIn Clock                                               |     |

| 8.1.2: EJ_TCK Clock                                                 |     |

| 8.1.3: Handling Clock Insertion Delay                               | 100 |

| 8.2: AHB Bus Clock                                                  |     |

| 8.2.1: SI_AHBStb to enable lower AHB Bus Clock Ratio                | 101 |

| 8.2.2: Waveforms and Timing Requirements for fixed AHB Clock Ratios | 101 |

| 8.2.3: System Static Timing Analysis for AHB Clock Domain           |     |

| 8.3: Reset and Hardware Initialization                              |     |

| 8.3.1: SI ColdReset                                                 |     |

| 8.3.2: SI_Reset                                                     |     |

| 8.3.3: SI_NMI                                                       |     |

| 8.3.4: EJ_TRST_N                                                    |     |

| 8.4: Power Management                                               |     |

| 8.4.1: Reducing SI_ClkIn Frequency                                  |     |

| 8.4.2: Software-Induced Sleep Mode                                  |     |

| Chapter 9: Design For Test Features                                 |     |

| 9.1: Introduction                                                   |     |

| 9.2: Scan Test                                                      |     |

| 9.3: Integrated RAM BIST                                            |     |

| 9.3.1: RAM BIST-related Interface Signals                           |     |

| 9.3.2: RAM BIST Signal Waveform for a Memory Test                   |     |

| 9.3.3: Number of Cycles for Memory BIST                             |     |

| 9.4: User-Specific RAM BIST                                         |     |

| Appendix A: References                                              | 113 |

| Appendix B: Revision History                                        | 115 |

## **List of Figures**

| Figure 2.1: Top-level RTL Hierarchy                                             | . 13 |

|---------------------------------------------------------------------------------|------|

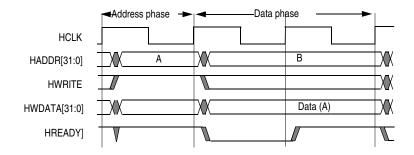

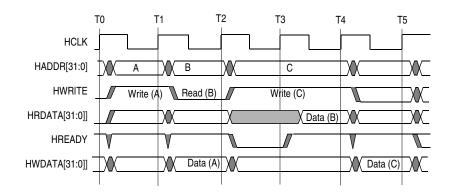

| Figure 3.1: Read Transfer with no Wait States                                   | . 30 |

| Figure 3.2: Write Transfer with no Wait States                                  | . 30 |

| Figure 3.3: Read Transfer with Two Wait States                                  | . 30 |

| Figure 3.4: Write Transfer with One Wait State                                  | . 31 |

| Figure 3.5: Multiple Transfers                                                  |      |

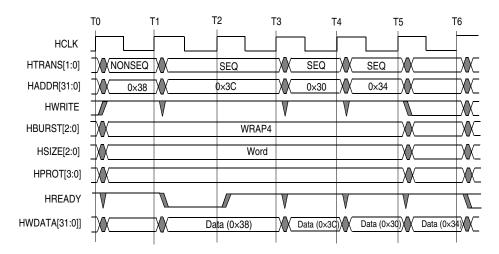

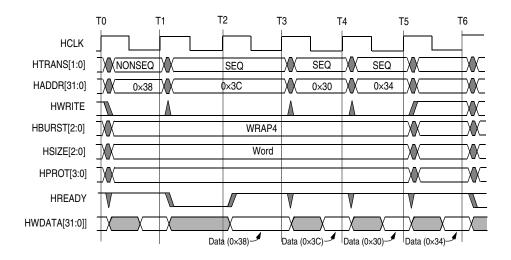

| Figure 3.6: Four-Beat Wrapping Burst of Write Transfer                          |      |

| Figure 3.7: Four-Beat Wrapping Burst of Read Transfer                           | . 33 |

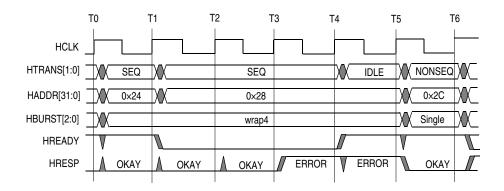

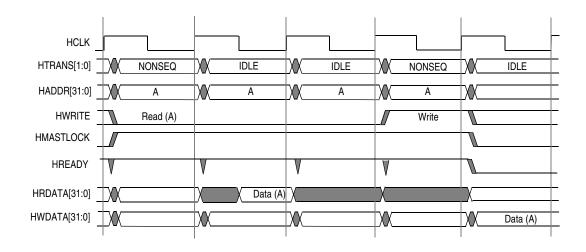

| Figure 3.8: Address Changes During a Waited Transfer After an ERROR             |      |

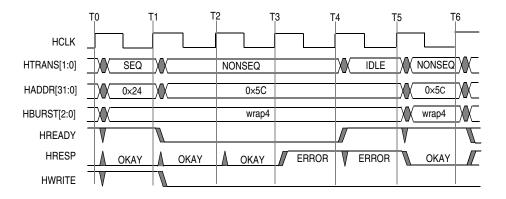

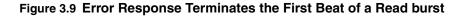

| Figure 3.9: Error Response Terminates the First Beat of a Read burst            | . 34 |

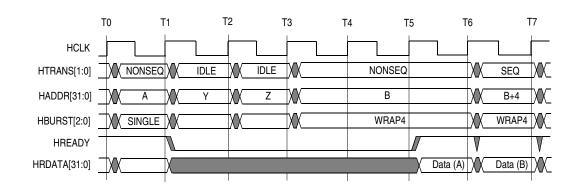

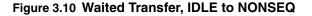

| Figure 3.10: Waited Transfer, IDLE to NONSEQ                                    | . 35 |

| Figure 3.11: Locked Transfer                                                    |      |

| Figure 3.12: HMASTLOCK was deasserted by the ERROR response of Read Sequence    | . 36 |

| Figure 4.1: EIC Interrupt Signals                                               |      |

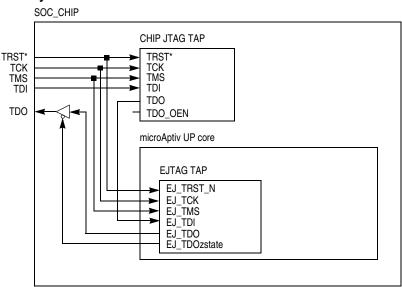

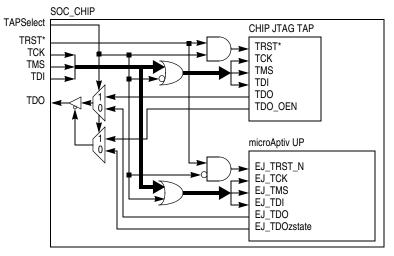

| Figure 5.1: Daisy-Chained TDI-TDO Between JTAG and EJTAG TAP Controllers        |      |

| Figure 5.2: Multiplexing Between JTAG and EJTAG TAP Controllers                 | . 48 |

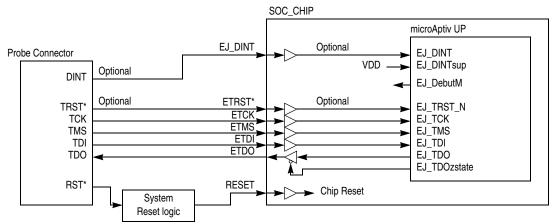

| Figure 5.3: EJTAG Chip-Level Pin Connection                                     |      |

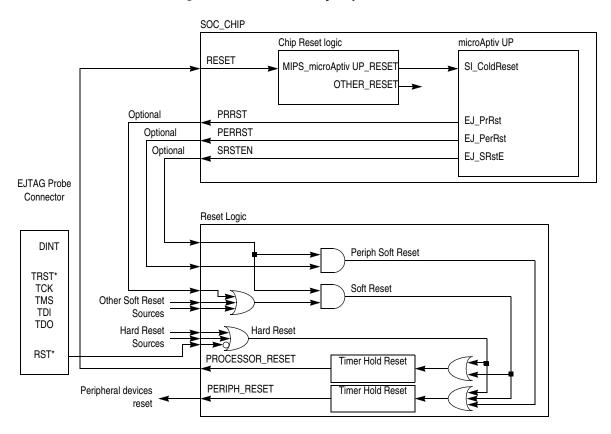

| Figure 5.4: Reset Circuitry Implementation                                      |      |

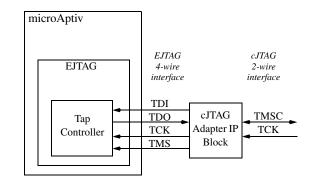

| Figure 5.5: cJTAG Interface                                                     |      |

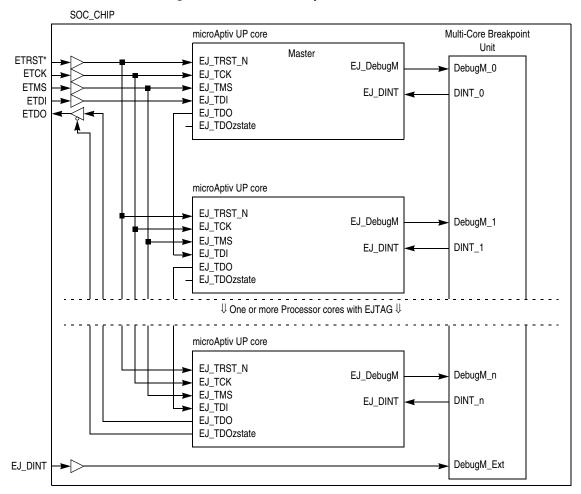

| Figure 5.6: Multi-Core Implementation                                           |      |

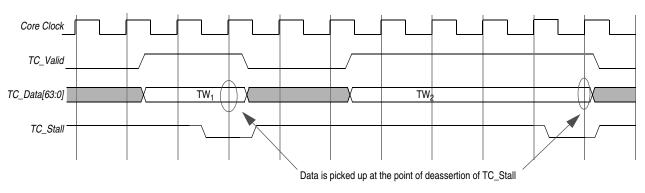

| Figure 5.7: TC_Valid and TC_Stall Timing                                        |      |

| Figure 6.1: General Transfer Example                                            |      |

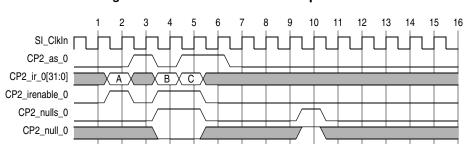

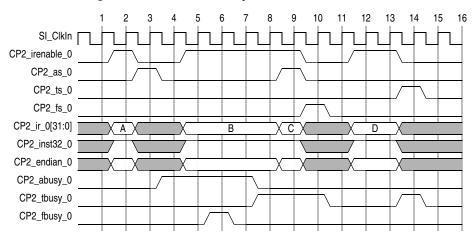

| Figure 6.2: Instruction Dispatch Waveforms                                      |      |

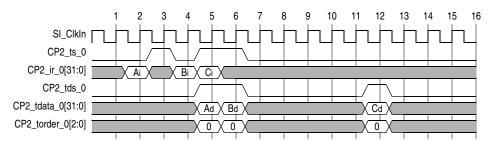

| Figure 6.3: To Coprocessor Data Waveforms                                       |      |

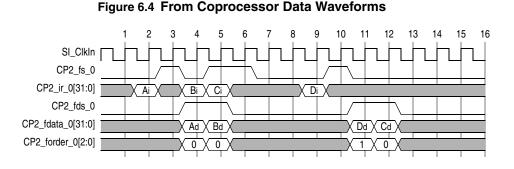

| Figure 6.4: From Coprocessor Data Waveforms                                     |      |

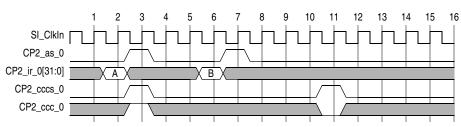

| Figure 6.5: Condition Code Check Waveforms                                      |      |

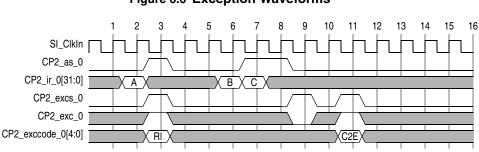

| Figure 6.6: Exception Waveforms                                                 |      |

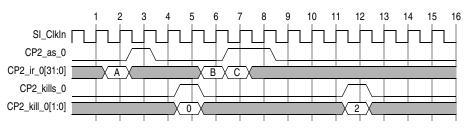

| Figure 6.7: Instruction Killing Waveforms                                       |      |

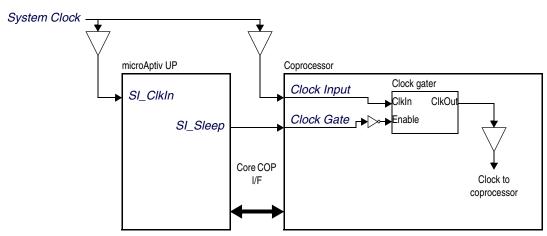

| Figure 6.8: Use of SI_Sleep for Clock-Gating in the Coprocessor                 |      |

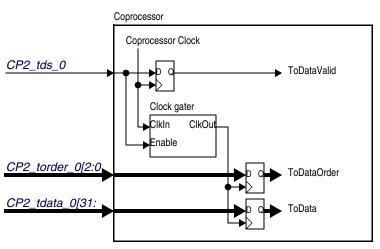

| Figure 6.9: Clock-Gating of To Data Registers in Coprocessor                    |      |

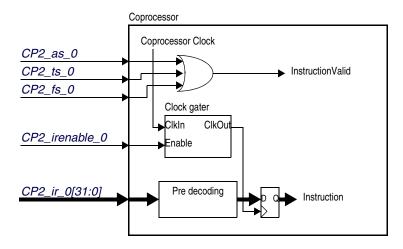

| Figure 6.10: Clock Gating of Instruction Registers in Coprocessor               |      |

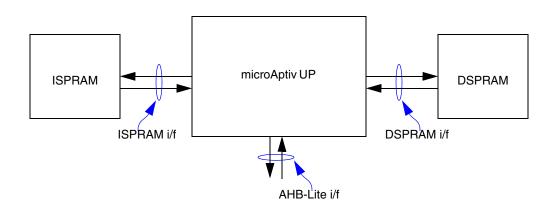

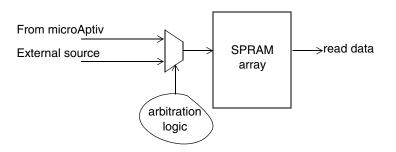

| Figure 7.1: Basic SPRAM Block Diagram                                           |      |

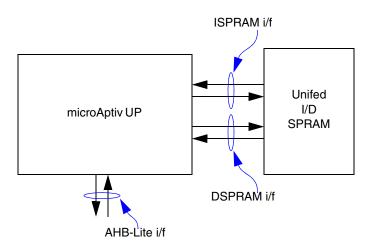

| Figure 7.2: Unified I/D SPRAM Block Diagram                                     |      |

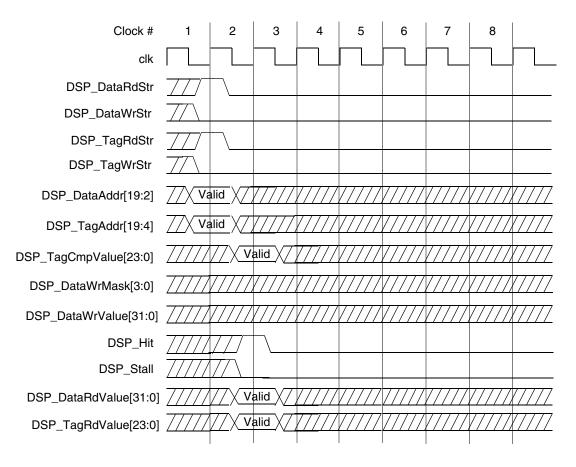

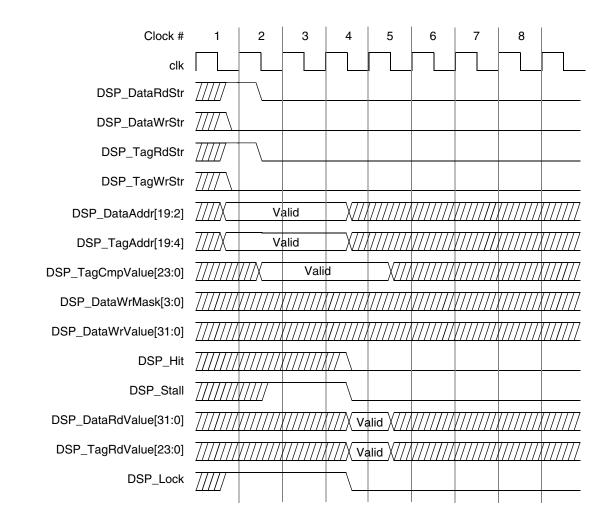

| Figure 7.3: Single DSPRAM Read                                                  |      |

| Figure 7.4: Single Multi-Cycle DSPRAM Read                                      |      |

| Figure 7.5: Single DSPRAM Write                                                 |      |

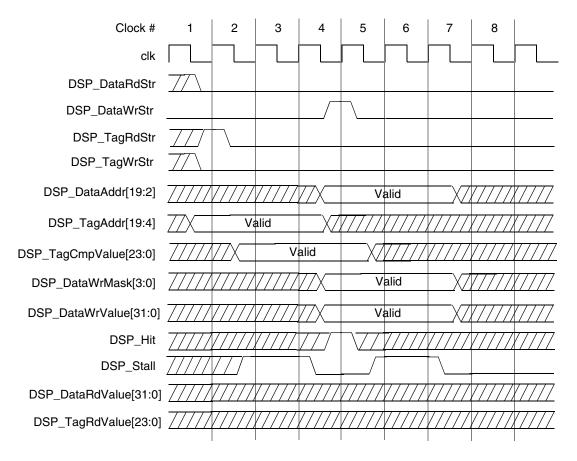

| Figure 7.6: Single Multi-Cycle DSPRAM Write                                     |      |

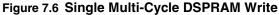

| Figure 7.7: Combined DSPRAM Tag Read and Data Write                             |      |

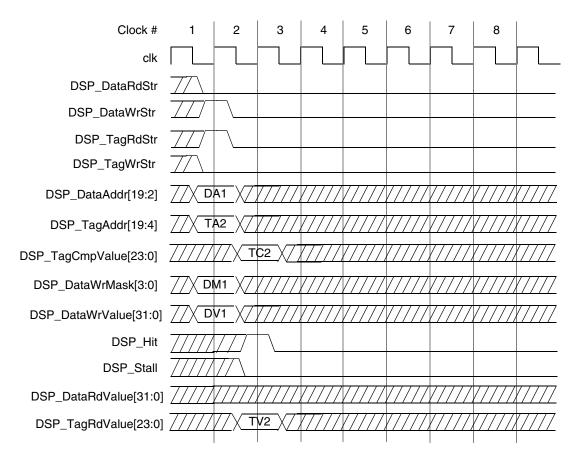

| Figure 7.8: Consecutive DSPRAM Reads                                            |      |

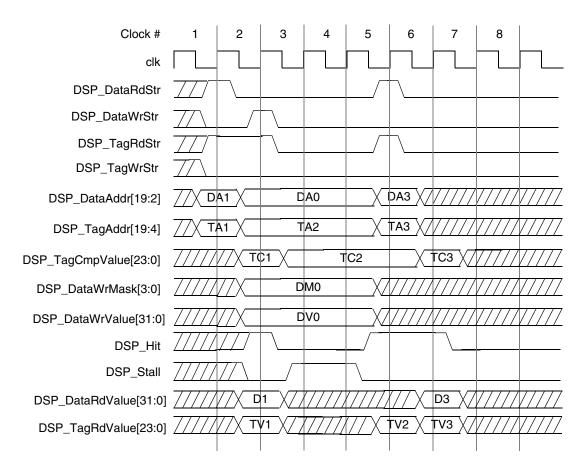

| Figure 7.9: Read-Write-Read                                                     |      |

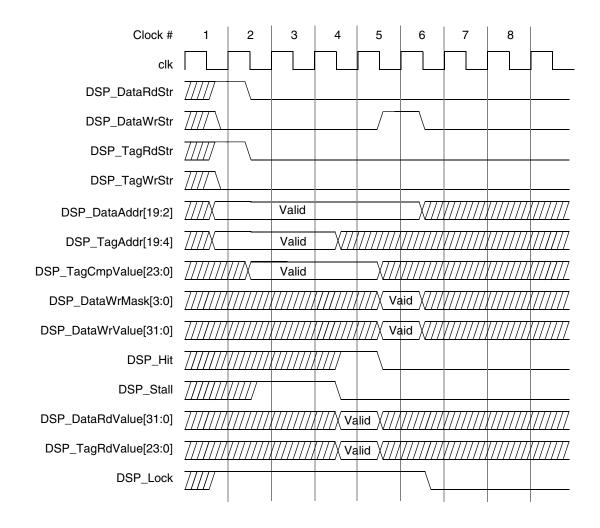

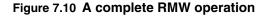

| Figure 7.10: A complete RMW operation                                           |      |

| Figure 7.11: A Store operation followed by an atomic operation in DSPRAM access |      |

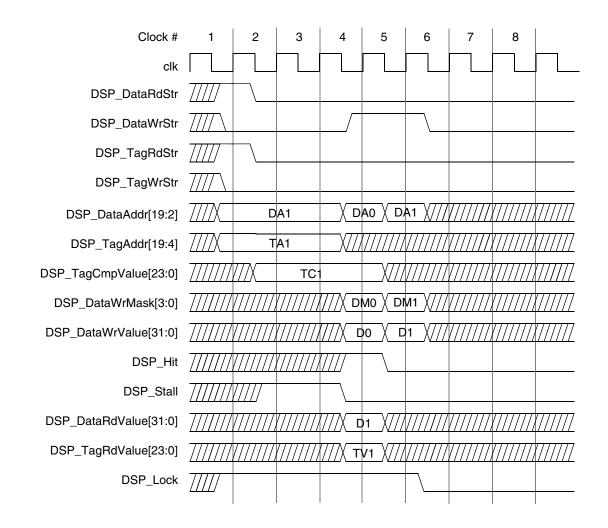

| Figure 7.12: RMW Operation does not hit in DSPRAM                               |      |

| Figure 7.13: External Access to Single-ported SPRAM                             |      |

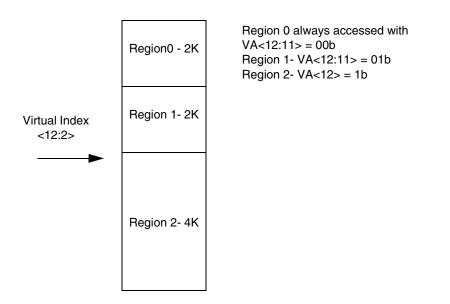

| Figure 7.14: Multiple SPRAM Regions                                             |      |

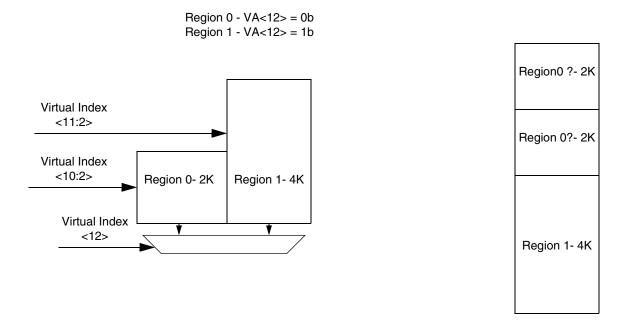

| Figure 7.15: Multiple SPRAM Regions in Separate Arrays                          |      |

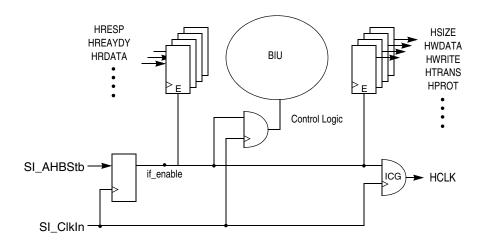

| Figure 8.1: SI_AHBStb enables AHB bus clock ratio                               | 101  |

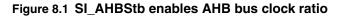

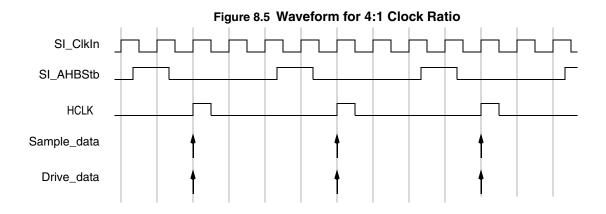

| Figure 8.2: Waveform for 1:1 Clock Ratio                               |     |

|------------------------------------------------------------------------|-----|

| Figure 8.3: Waveform for 2:1 Clock Ratio                               |     |

| Figure 8.4: Waveform for 3:1 Clock Ratio                               | 102 |

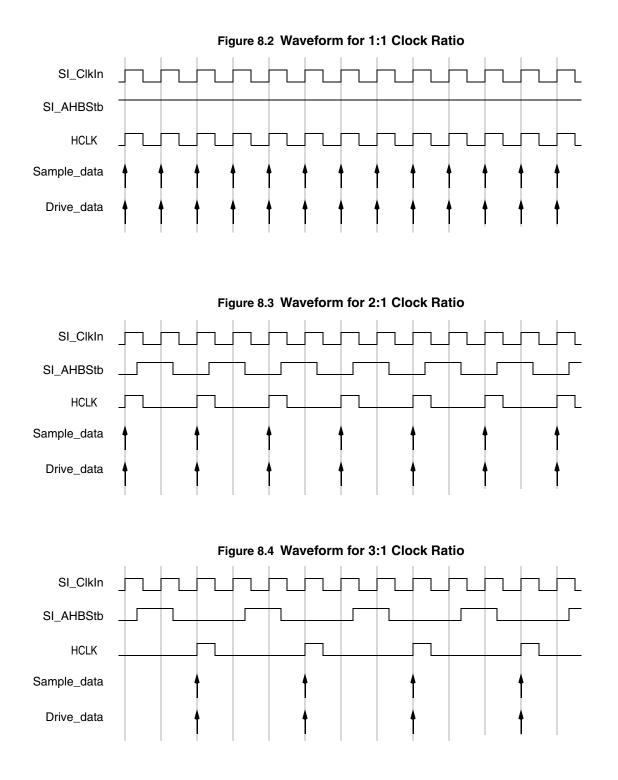

| Figure 8.5: Waveform for 4:1 Clock Ratio                               | 103 |

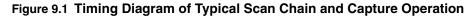

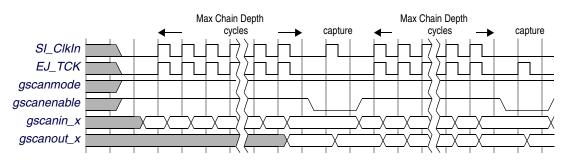

| Figure 9.1: Timing Diagram of Typical Scan Chain and Capture Operation | 108 |

| Figure 9.2: RAM BIST I/O Signals Timing                                | 110 |

## **List of Tables**

| Table 2.1: Signal Type Key                                                            |     |

|---------------------------------------------------------------------------------------|-----|

| Table 2.1: Signal Type Key         Table 2.2: Signal Prefix Key                       |     |

| Table 2.3: Signal Descriptions for m14k_cpu Level                                     | 14  |

| Table 2.4: Signals on m14k_top for External Interface to Custom Blocks                |     |

| Table 3.1: Transfer Types                                                             | 31  |

| Table 3.2: Transfer Size                                                              | 32  |

| Table 3.3: Burst Operation Types                                                      | 32  |

| Table 3.4: Sequence Order for 4-beat wrapping burst of word                           | 33  |

| Table 3.5: Protection Control                                                         |     |

| Table 4.1: Interrupt Signals in Compatibility and Vectored Modes                      |     |

| Table 4.2: Interrupt Signals in EIC Mode                                              | 42  |

| Table 6.1: Supported Coprocessor 2 instructions                                       |     |

| Table 6.2: Transfers Required for Each Dispatch                                       | 61  |

| Table 6.3: Allowable Interface Latencies from a Coprocessor to the microAptiv UP Core | 62  |

| Table 6.4: Interface Latencies from the microAptiv UP Core to a Coprocessor           | 63  |

| Table 7.1: SPRAM Interface Cycle Timing                                               |     |

| Table 7.2: Read and Write Width for SPRAM Arrays                                      | 80  |

| Table 7.3: Byte Control for DSPRAM Writes.                                            | 81  |

| Table 7.4: SPRAM Transaction Types                                                    | 83  |

| Table 7.5: ISPRAM Connection to DSPRAM Ports                                          |     |

| Table 9.1: Core Input Values for Major Operating Modes                                | 107 |

| Table 9.2: Fail Signals                                                               |     |

|                                                                                       |     |

Chapter 1

## Overview

This document is targeted for the ASIC designer who is integrating a version of the MIPS32® microAptiv<sup>TM</sup> UP processor core into the system ASIC. This document is applicable both to those integrators who are using a hard core and those who are integrating a soft core.

In addition to this overview chapter, the document contains the following chapters:

- Chapter 2, "Signal Descriptions" on page 11 describes the pins of the core.

- Chapter 3, "AHB-Lite Interface" on page 29 describes the AHB-Lite interface protocol used by the core.

- Chapter 4, "Interrupt Interface" on page 39 describes the signalling in different interrupt modes.

- Chapter 5, "EJTAG Interface" on page 45 discusses the EJTAG interface used by the core, including the optional EJTAG TAP controller and the trace interface.

- Chapter 6, "Coprocessor Interface" on page 57 describes the Coprocessor 2 interface and protocol used by the core.

- Chapter 7, "Scratchpad RAM Interface" on page 75 describes the Scratchpad RAM interface that may optionally be present on the core.

- Chapter 8, "Clocking, Reset, and Power" on page 99 covers issues related to handling the clock insertion delay of the microAptiv UP core. Additionally, the hardware reset requirements of the core, as well as power management techniques, are discussed.

- Chapter 9, "Design For Test Features" on page 107 discusses general DFT features which may be present on the microAptiv UP core. Details are specific to a particular implementation of the core.

### **1.1 Environment Variable Setup**

Some UNIX paths described in the document refer to *MIPS\_HOME*, *MIPS\_CORE* and *MIPS\_PROJECT* environment variables. See the "Release Deliverables and Installation" chapter of the System Package & Simulation Flow User's Manual [5] for more information on defining required environment variables.

#### 1.1.1 microAptiv UP Deliverables

All of the microAptiv UP deliverables packages include the following:

• Cycle-exact model: An encrypted, cycle-exact version of the RTL model is generated using VMC from Synopsys and included in every release. This model is intended mainly for hard-core customers who do not receive the source RTL, but is available for soft-core customers if desired. The VMC model is also used within the supplied verification testbench. Use of the cycle-accurate model is currently limited to x86 RedHat Linux platforms.

MIPS32® microAptiv<sup>™</sup> UP Processor Core Family Integrator's Guide, Revision 01.01

#### **IMAGINATION TECHNOLOGIES PROPRIETARY / CONFIDENTIAL**

• Functional simulation: The testbench code is written in Verilog. The simulation environment includes support for the following Verilog simulators: NC-Verilog from Cadence, VCS from Synopsys, and ModelSim from Mentor Graphics.

Soft core deliverables packages will also include support for the following

- RTL: The core RTL code is written in Verilog. The simulation environment includes support for the Verilog simulators listed above. Simulation is supported at both the RTL and gate levels.

- Implementation scripts: synthesis, timing analysis, power analysis, scan insertion, ATPG, equivalence checking, physical design. The MIPS® Physical Design Guide [1]describes the scripts as well as the tools and versions that are supported.

No tool requirements are dictated for the back-end EDA tools that may be used to create a physical implementation of the microAptiv UP core.

### **1.2 Other Documents**

Other documents available from MIPS cover additional aspects of an microAptiv UP core, including the software view of the core, programming guidelines, and general details about certain sub-interfaces. If these other documents are referenced within this *Integrator's Guide*, they are listed in Appendix A, "References" on page 113.

Chapter 2

## **Signal Descriptions**

This chapter describes the signals on a MIPS32 microAptiv UP processor core. Only naming conventions and actual signal names are listed in this chapter. The specific interface protocols to which each signal adheres are described in subsequent chapters.

This chapter contains the following sections:

- Section 2.1 "Naming Conventions"

- Section 2.2 "Top-level Hierarchy"

- Section 2.3 "Detailed Signal Descriptions"

## 2.1 Naming Conventions

The signal direction key for the signal descriptions is shown in Table 2.1 below.

| Туре | Description                                                                                                                                                                                |

|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| In   | Input to the core, unless otherwise noted, sampled on the rising edge of the appropriate clock sig-<br>nal.                                                                                |

| Out  | Output of the core, unless otherwise noted, driven at the rising edge of the appropriate clock sig-<br>nal.                                                                                |

| AIn  | Asynchronous inputs that are synchronized by the core.                                                                                                                                     |

| SIn  | Static input to the core. These signals control configuration options and are normally tied to either power or ground. They must not change state while <i>SI_ColdReset</i> is deasserted. |

| SOut | Static output from the core. These signals control configuration options in an optional connected Coprocessor 2. These signals are static and never change state.                          |

#### Table 2.1 Signal Type Key

The names of interface signals present on an microAptiv UP core are prefixed with a unique string, according to their primary function. Table 2.2 defines the prefixes used for microAptiv UP core interface signals.

#### Table 2.2 Signal Prefix Key

| Prefix | Description                                                                    |

|--------|--------------------------------------------------------------------------------|

| H_     | Signals directly related to the AHB-Lite interface.                            |

| SI_    | General system interface signals, which are not part of theAHB-Lite interface. |

| EJ_    | Signals related to the EJTAG interface.                                        |

| TC_    | Signals related to the EJTAG Trace interface.                                  |

| CP2_   | Signals related to the Coprocessor 2 interface.                                |

MIPS32® microAptiv<sup>™</sup> UP Processor Core Family Integrator's Guide, Revision 01.01

#### **IMAGINATION TECHNOLOGIES PROPRIETARY / CONFIDENTIAL**

| Prefix     | Description                                                                                               |

|------------|-----------------------------------------------------------------------------------------------------------|

| UDI_       | Signals related to the CorExtend user-defined instruction interface (Pro Series <sup>™</sup> cores only). |

| {I,D}SP_   | Instruction/Data ScratchPad RAM interfaces                                                                |

| PM_        | Performance monitoring signals                                                                            |

| gscan/Bist | Signals related to design-for-test features, either scan or memory Built-In-Self-Test (BIST).             |

| gmb        | Signals related to integrated memory BIST.                                                                |

#### Table 2.2 Signal Prefix Key (Continued)

Generally, most signals have active-high assertion levels if not otherwise specified in the tables. Signals ending in the suffix " $_N$ " are active low.

## 2.2 Top-level Hierarchy

An microAptiv UP processor core has two options for the top-level module when the core is implemented. The choice of top-level module depends on implementation trade-offs when the core is synthesized or hardened, and the choice affects the top-level pinout visible when the core is integrated into the chip.

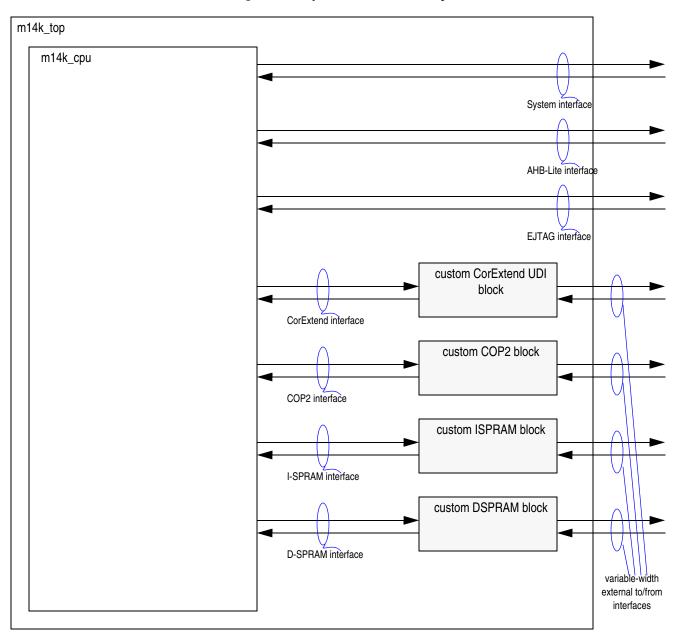

The top-level hierarchy is shown in Figure 2.1. Either module  $m14k\_cpu$  or module  $m14k\_top$  can be chosen as the top-level module at build time. Module  $m14k\_cpu$  represents the direct processor core. Module  $m14k\_top$  encapsulates  $m14k\_cpu$  as well as some user-definable modules that interact tightly with  $m14k\_cpu$  and can be customized by a user.

TheAHB-Lite, system, EJTAG, trace and testability interfaces exist on both the  $m14k\_cpu$  and  $m14k\_top$  levels, with the expectation that any logic interacting with these interfaces lies in system logic above  $m14k\_top$ . Thescratchpad RAM, Coprocessor 2 and CorExtend interfaces are present on the  $m14k\_cpu$  level only. These interfaces are closely coupled to the processor pipeline. Custom logic connected to these interfaces can be combined with the processor core itself at synthesis time. In this case, synthesis can be performed at the  $m14k\_top$  level to minimize the need for defining detailed constraints between the CPU and the custom logic, and to allow synthesis to better optimize the interfaces. External system logic can still interact with the custom blocks via the configurable width to/from busses shown in Figure 2.1, with no direct changes needed to the m14k\\_top module RTL.

In some designs, however, the custom logic may not be known when the core is built and will be added later. For this situation, synthesis at the m14k\_cpu level is appropriate. The custom interfaces need to be constrained for their expected use, but custom logic can be added later.

When integrating a previously hardened microAptiv UP core, consult with the provider of the core to determine whether it was built with  $m14k_top$  or  $m14k_cpu$  as the top level.

Figure 2.1 Top-level RTL Hierarchy

## 2.3 Detailed Signal Descriptions

All core signals at the  $m14k\_cpu$  level are listed in Table 2.3 below. The following table, Table 2.4, lists the variable width to/from signals on the  $m14k\_top$  level that allow external access to internal custom blocks for thescratchpad RAM, Coprocessor 2 and CorExtend interfaces.

Note that the signals are grouped by logical function, not by expected physical location. All signals, with the exception of *EJ\_TRST\_N*, are active-high signals. *EJ\_DINT* and *SI\_NMI* go through edge-detection logic so that only one exception is taken each time they are asserted.

## 2.3.1 Signals at m14k\_cpu Level

Table 2.3 describes the signals at the m14k\_cpu level of hierarchy.

| Signal Name                     | Туре          | Description                                                                                                                                                                                                                                                                                                                   |

|---------------------------------|---------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| System Interface: Refer to Cha  | pter 8, "Cloc | king, Reset, and Power" on page 99 for more details                                                                                                                                                                                                                                                                           |

| Clock Signals: Refer to 8.1 "Cl | ocking" on p  | age 99 for more details                                                                                                                                                                                                                                                                                                       |

| SI_ClkIn                        | In            | Clock input. All inputs and outputs, except a few of the EJTAG signals, are sampled or asserted relative to the rising edge of this signal.                                                                                                                                                                                   |

| SI_ClkOut                       | Out           | Reference clock. This free running clock signal provides a reference for de-skewing any clock insertion delay created by the internal clock buffering in the core.                                                                                                                                                            |

| Reset Signals: Refer to 8.4 "Po | wer Manager   | nent" on page 104 for a description of the various types of reset.                                                                                                                                                                                                                                                            |

| SI_BootExcISAMode               | AIn           | When set to '0', boot up from MIPS32 mode or, set to '1' to boot in microMIPS mode                                                                                                                                                                                                                                            |

| SI_ColdReset                    | AIn           | Hard/Cold reset signal. Causes a Reset Exception in the core.                                                                                                                                                                                                                                                                 |

| SI_NMI                          | AIn           | Non-maskable Interrupt. An edge detect is used on this signal. When this signal is sampled asserted (high) one clock after being sampled deasserted, an NMI is posted to the core.                                                                                                                                            |

| SI_Reset                        | AIn           | Soft/Warm reset signal. Causes a SoftReset Exception in the core.                                                                                                                                                                                                                                                             |

| Power Management Signals: Se    | e 8.4 "Powe   | r Management" on page 104 for more details                                                                                                                                                                                                                                                                                    |

| SI_ERL                          | Out           | This signal reflects the state of the ERL bit (2) in the CP0 <i>Status</i> register and indicates the error level. The core asserts <i>SI_ERL</i> whenever a Reset, Soft Reset, or NMI exception is taken.                                                                                                                    |

| SI_EXL                          | Out           | This signal reflects the state of the EXL bit (1) in the CP0 <i>Status</i> register and indicates the exception level. The core asserts <i>SI_EXL</i> whenever any exception other than a Reset, Soft Reset, NMI, or Debug exception is taken.                                                                                |

| SI_NESTERL                      | Out           | This signal reflects the state of the ERL bit (2) in the CP0 <i>NestedExc</i> register.                                                                                                                                                                                                                                       |

| SI_NESTEXL                      | Out           | This signal reflects the state of the EXL bit (1) in the CP0 <i>NestedExc</i> register.                                                                                                                                                                                                                                       |

| SI_RP                           | Out           | This signal reflects the state of the RP bit (27) in the CP0 <i>Status</i> register. Software can write this bit to indicate that the device can enter a reduced power mode.                                                                                                                                                  |

| SI_Sleep                        | Out           | This signal is asserted by the core whenever the WAIT instruction is executed.<br>The assertion of this signal indicates that the clock has stopped and that the core<br>is waiting for an interrupt.                                                                                                                         |

| Break Status Signals:           |               |                                                                                                                                                                                                                                                                                                                               |

| SI_lbs[7:0]                     | Out           | Reflects state of breakpoint status (BS) field in the Instruction Breakpoint Status (IBS) register. These bits are set when the corresponding break condition has matched, for breaks enabled as either a breakpoints or trigger points. If fewer than 6 instruction breakpoints exist, the unimplemented bits are tied to 0. |

| SI_Dbs[3:0]                     | Out           | Reflects state of breakpoint status (BS) field in the Data Breakpoint Status (DBS) register. These bits are set when the corresponding break condition has matched, for breaks enabled as either a breakpoints or trigger points. If fewer than 2 data breakpoints exist, the unimplemented bits are tied to 0.               |

| Interrupt Signals:              | •             |                                                                                                                                                                                                                                                                                                                               |

### Table 2.3 Signal Descriptions for m14k\_cpu Level

| Signal Name       | Туре   | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|-------------------|--------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SI_EICPresent     | SIn    | Indicates whether an external interrupt controller is present. Value is visible to software in the $Config3_{VEIC}$ register field.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| SI_EICVector[5:0] | In     | Provides the vector number for an interrupt request in External Interrupt Control-<br>ler (EIC) mode. (Note: This input decouples the interrupt priority from the vector<br>offset. For compatibility with earlier Release 2 cores in EIC mode, connect<br><i>SI_Int[7:0]</i> and <i>SI_EICVector[5:0]</i> together.)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| SI_EISS[3:0]      | In     | General purpose register shadow set number to be used when servicing an inter-<br>rupt in EIC interrupt mode.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

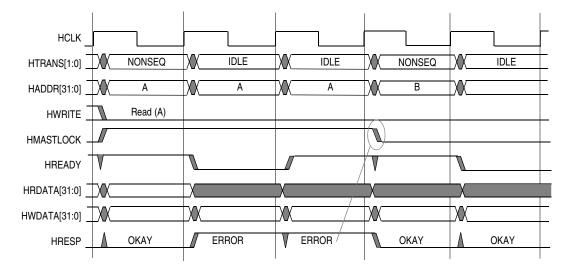

| SI_IAck           | Out    | Interrupt acknowledge indication for use in external interrupt controller mode. This signal is active for a single $SI\_Clkln$ cycle when an interrupt is taken. When the processor initiates the interrupt exception, it loads the value of the $SI\_Int[7:0]$ pins into the $Cause_{RIPL}$ field (overlaid with $Cause_{IP9\_IP2}$ ), and signals the external interrupt controller to notify it that the current interrupt request is being serviced. This allows the controller to advance to another pending higher-priority interrupt, if desired.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| SI_Int[7:0]       | In/AIn | <ul> <li>Active high Interrupt pins. These signals are driven by external logic and when asserted indicate an interrupt exception to the core. The interpretation of these signals depends on the interrupt mode in which the core is operating; the interrupt mode is selected by software.</li> <li>The <i>Sl_Int</i> signals go through synchronization logic and can be asserted asynchronously to <i>Sl_ClkIn</i>. In External Interrupt Controller (EIC) mode, however, the interrupt pins are interpreted as an encoded value, so they must be asserted synchronously to <i>Sl_ClkIn</i> to guarantee that all bits are received by the core in a particular cycle.</li> <li>The interrupt pins are level sensitive and should remain asserted until the interrupt has been serviced.</li> <li>In Release 1 Interrupt Compatibility mode:</li> <li>All 8 interrupt pins have the same priority as far as the hardware is concerned.</li> <li>Interrupts are non-vectored.</li> <li>In Vectored Interrupt (VI) mode:</li> <li>The <i>Sl_Int</i> pins are interpreted as individual hardware interrupt requests.</li> <li>Internally, the core prioritizes the hardware interrupts and chooses an interrupt vector.</li> <li>In External Interrupt Controller (EIC) mode:</li> <li>An external block prioritizes its various interrupt requests and produces a vector number of the highest priority interrupt to be serviced.</li> <li>The vector number is driven on the <i>Sl_Int</i> pins, and is treated as an 8-bit encoded value in the range of 0255.</li> <li>When the core starts the interrupt exception, signaled by the assertion of <i>Sl_IAck</i>, it loads the value of the <i>Sl_Int</i>?:0] pins into the <i>Cause<sub>RIPL</sub></i> field (overlaid with <i>Cause<sub>IP9.IP2</sub></i>). The interrupt controller can then signal another interrupt.</li> </ul> |

| SI_ION[17:1]      | Out    | Interrupt Offset Number. Indicates the current interrupt offset number that is being serviced. The offset number was captured from <i>SI_Offset</i> [17:1] when <i>SI_Int</i> was asserted to request an interrupt exception. Depending on the configuration of the EIC, <i>SI_ION</i> [17:1] may be updated when <i>SI_IAck</i> is asserted, .                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| SI_IPL[7:0]       | Out    | Current interrupt priority level from the $Cause_{IPL}$ register field, provided for use<br>by an external interrupt controller. This value is updated whenever $SI_IAck$ is<br>asserted.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| Table 2.3 Signal Descriptions | s for m14k_cpu Level (Co | ontinued) |

|-------------------------------|--------------------------|-----------|

|-------------------------------|--------------------------|-----------|

| Signal Name                  | Туре |                                       |                                                                                      | Description                                                                                                                                                                                                                 |         |

|------------------------------|------|---------------------------------------|--------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|

| SI_IPTI[2:0]                 | SIn  |                                       |                                                                                      | The timer interrupt is combined with the software in the <i>IntCtl<sub>IPTI</sub></i> register finds the <i>IntCtl</i>                                                                                                      |         |

|                              |      |                                       | SI_IPTI                                                                              | Combined w/ SI_Int                                                                                                                                                                                                          |         |

|                              |      | -                                     | 0-1                                                                                  | None                                                                                                                                                                                                                        |         |

|                              |      | -                                     | 2                                                                                    | SI_Int[0]                                                                                                                                                                                                                   |         |

|                              |      |                                       | 3                                                                                    | SI_Int[1]                                                                                                                                                                                                                   |         |

|                              |      |                                       | 4                                                                                    | SI_Int[2]                                                                                                                                                                                                                   |         |

|                              |      | _                                     | 5                                                                                    | SI_int[3]                                                                                                                                                                                                                   |         |

|                              |      | -                                     | 6                                                                                    | SI_Int[4]                                                                                                                                                                                                                   |         |

|                              |      |                                       | 7                                                                                    | SI_Int[5]                                                                                                                                                                                                                   |         |

| SI_IVN[5:0]                  | Out  | being ser<br>SI_Int is<br>figuration  | viced. This vector num<br>asserted to request for<br>h, <i>SI_IVN[5:0]</i> is update | dicate the current interrupt vector number<br>ber was captured from <i>SI_EICVector</i> [5:0]<br>an interrupt exception. Depends on the EI<br>ted when <i>SI_IAck</i> is asserted.                                          | when    |

| SI_NMITaken                  | Out  | NMI Tak                               | en reflects the value of                                                             | CP0 register STATUS.NMITaken.                                                                                                                                                                                               |         |

| SI_Offset[17:1]              | In   | Offset for                            | r interrupt vector                                                                   |                                                                                                                                                                                                                             |         |

| SI_SWInt[1:0]                | Out  |                                       |                                                                                      | the signals represent the value in the <i>IP[1:0]</i> provided for use by an external interrupt c                                                                                                                           |         |

| SI_TimerInt                  | Out  | Compar                                | e registers match and i                                                              | signal is asserted whenever the <i>Count</i> and s deasserted when the <i>Compare</i> register is the value of the <i>Cause<sub>TI</sub></i> register field.                                                                |         |

|                              |      | Tradition pins. How                   | ally, <i>SI_TimerInt</i> is fe                                                       | ibility mode or Vectored Interrupt mode:<br>d back into the core through one of the interneeded, as the core will internally route the<br>IntCtl.IPTI field.                                                                |         |

|                              |      | The <i>SI_7</i> then prior controller | ritizes the timer interru                                                            | r (EIC) mode:<br>ided to the external interrupt controller, wh<br>pt with all other interrupt sources, as desire<br>red interrupt value on the <i>SI_Int</i> pins. Sinc<br><i>SI_IPTI</i> pins are not meaningful in EIC mo | d. The  |

| Configuration Inputs/Outputs |      | u                                     |                                                                                      |                                                                                                                                                                                                                             |         |

| SI_CPUNum[9:0]               | SIn  | hardware<br>field, so i               | value specified on the                                                               | ndividual core in a multi-processor system<br>se pins is available in the <i>EBase<sub>CPUNum</sub></i> re<br>are to distinguish a particular processor. In<br>should be set to zero.                                       | egister |

| SI_Endian                    | SIn  | Indicates                             | -                                                                                    | the core. Value is visible to software in th                                                                                                                                                                                | e       |

|                              |      |                                       | SI_Endian                                                                            | Base Endian Mode                                                                                                                                                                                                            |         |

|                              |      |                                       | 0                                                                                    | Little Endian                                                                                                                                                                                                               |         |

|                              |      | 1                                     | 1                                                                                    | Big Endian                                                                                                                                                                                                                  |         |

| Signal Name                 | Туре          | De                                                                                                                                                                     | scription                                                                                                                                                                                                          |

|-----------------------------|---------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SI_MergeMode[1:0]           | SIn           |                                                                                                                                                                        | whether merging is allowed in the 16-byte<br><i>MergeMode[0]</i> is visible to software in the                                                                                                                     |

|                             |               | SI_MergeMode[1:0]                                                                                                                                                      | Merge Mode                                                                                                                                                                                                         |

|                             |               | 002                                                                                                                                                                    | No Merge                                                                                                                                                                                                           |

|                             |               | 012                                                                                                                                                                    | Reserved                                                                                                                                                                                                           |

|                             |               | 102                                                                                                                                                                    | Full Merge                                                                                                                                                                                                         |

|                             |               | 112                                                                                                                                                                    | Reserved                                                                                                                                                                                                           |

| SI_SRSDisable[3:0]          | SIn           | Disable use of some shadow register                                                                                                                                    | sets.                                                                                                                                                                                                              |

|                             |               | SI_SRSDisable[3:0]                                                                                                                                                     | Register Sets                                                                                                                                                                                                      |

|                             |               | 0000                                                                                                                                                                   | Use all register sets                                                                                                                                                                                              |

|                             |               | 1000                                                                                                                                                                   | Use 8 register sets                                                                                                                                                                                                |

|                             |               | 1100                                                                                                                                                                   | Use 4 register sets                                                                                                                                                                                                |

|                             |               | 1110                                                                                                                                                                   | Use 2 register sets                                                                                                                                                                                                |

|                             |               | 1111                                                                                                                                                                   | Use 1 register set                                                                                                                                                                                                 |

| SI_TraceDisable             | SIn           | Set to '1' to disable the trace hardwar                                                                                                                                | re.                                                                                                                                                                                                                |

| Fast Debug Channel:         |               |                                                                                                                                                                        |                                                                                                                                                                                                                    |

| SI_IPFDCI[2:0]              | In            | This input indicates which IP number nally in the core.                                                                                                                | r the FDC interrupt is combined with inter-                                                                                                                                                                        |

| SI_FDCInt                   | Out           | probe interrupt. Probe interrupt only<br>For External Interrupt Controller (EI<br>The <i>SI_FDCInt</i> signal is provided to<br>prioritizes the FDC interrupt with all | C) mode:<br>the external interrupt controller, which then<br>other interrupt sources, as desired. The con-<br>upt value on the <i>Sl_Int</i> pins. Since <i>Sl_Int</i> is                                          |

| Performance Counters:       |               |                                                                                                                                                                        |                                                                                                                                                                                                                    |

| SI_IPPCI[2:0]               | In            | This input indicates which IP number nally in the core.                                                                                                                | r the PCI interrupt is combined with inter-                                                                                                                                                                        |

| SI_PCInt                    | Out           | prioritizes the performance counter in<br>desired. The controller then encodes                                                                                         | C) mode:<br>he external interrupt controller, which then<br>nterrupt with all other interrupt sources, as<br>the desired interrupt value on the <i>SI_Int</i><br>I, the <i>SI_IPPCI</i> pins are not meaningful in |

| AHB-Lite Interface Refer to | Chapter 3, "A | HB-Lite Interface" on page 29 for mor                                                                                                                                  | e details.                                                                                                                                                                                                         |

| HADDR[31:0]                 | Out           | The 32-bit system address bus                                                                                                                                          |                                                                                                                                                                                                                    |

| HBURST[2:0]                 | Out           | Fixed length bursts of 4, 8, and 16 be                                                                                                                                 | r is a single transfer or forms part of a burst.<br>eats are spec'ed but not all are supported.<br>apping. Only Single or WRAP4 are sup-                                                                           |

| Signal Name                                                 | Туре                         | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|-------------------------------------------------------------|------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| HCLK                                                        | Out                          | The bus clock times all bus transfers. All signal timings are related to the rising edge of <i>HCLK</i> . It is a reference clock from the gated main clock <i>SI_ClkIn</i> .                                                                                                                                                                                                                                                                                                                                   |

| HMASTLOCK                                                   | Out                          | When HIGH, this signal indicates that the current transfer is part of a locked sequence. It has the same timing as the address and control signals. In the microAptiv UP core when atomic instruction access uncached space through AHB-Lite, assert <i>HMASTLOCK</i> until the atomic write transaction is broadcast on the AHB-Lite bus. Typically the locked transfer is used to maintain the integrity of a semaphore.                                                                                      |

| HPROT[3:0]                                                  | Out                          | The protection control signals provide additional information about a bus access<br>and are primarily intended for use by any module that wants to implement some<br>level of protection.<br><i>HPROT[3:1]</i> is set default to b001 because the microAptiv UP core can not pro-<br>vide the accuracy of all protection information. But <i>HPROT[0]</i> is used to distin-<br>guish between Opcode fetch and Data access. <i>HPROT=</i> 4'b0010 for instruction<br>fetches; 4'b0011 for data loads and stores |

| HRDATA[31:0]                                                | In                           | Read Data                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |