# **WAVE**

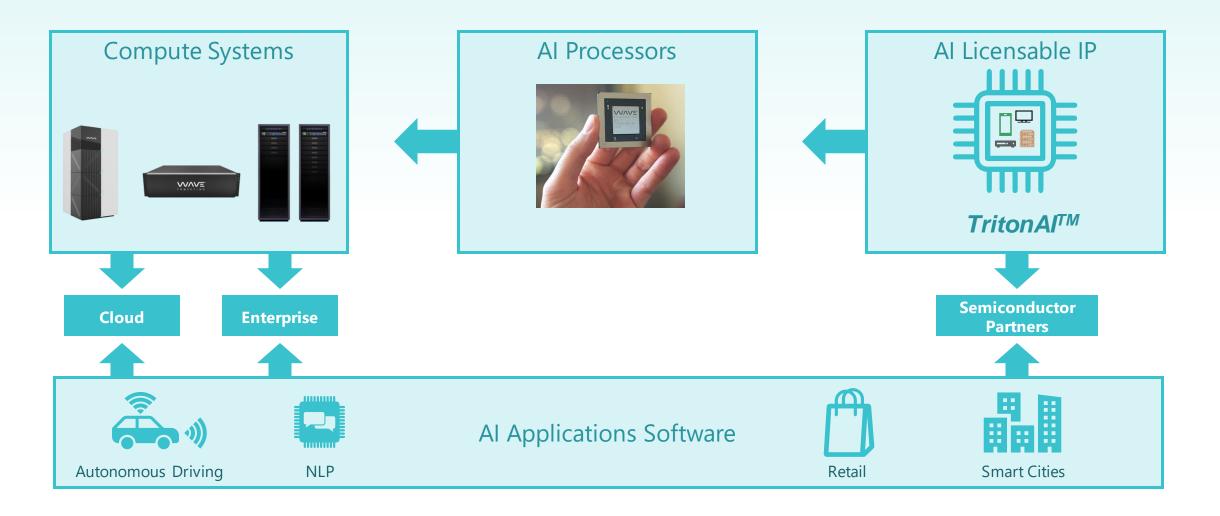

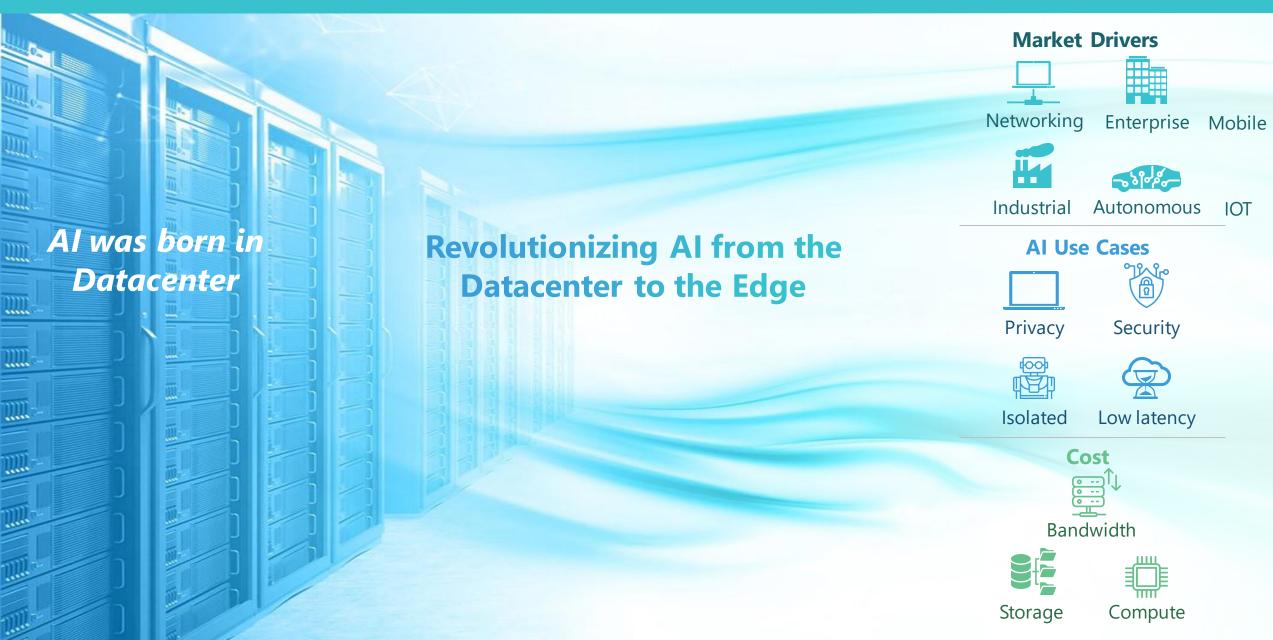

C O M P U T I N G Revolutionizing AI from the Datacenter to the Edge

Adapting the Wave Dataflow Architecture to a Licensable AI IP Product

Presented by **Yuri Panchul**, MIPS Open Technical Lead On SKOLKOVO Robotics & Al Conference. April 15-16, 2019 <u>www.wavecomp.ai</u>

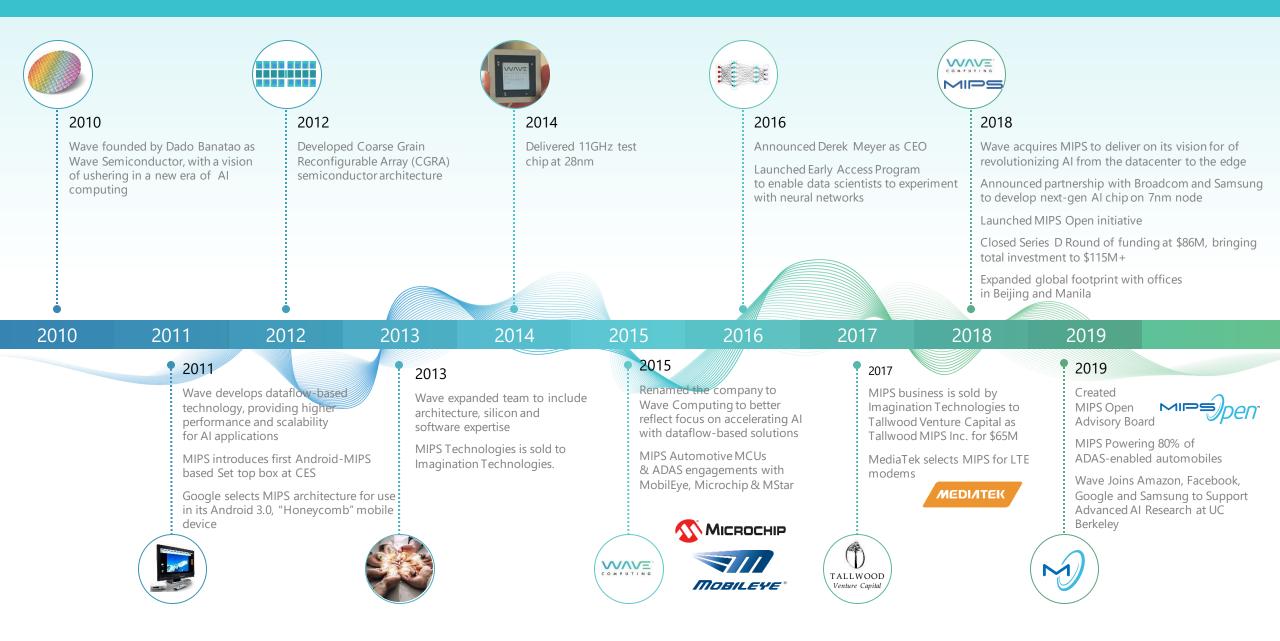

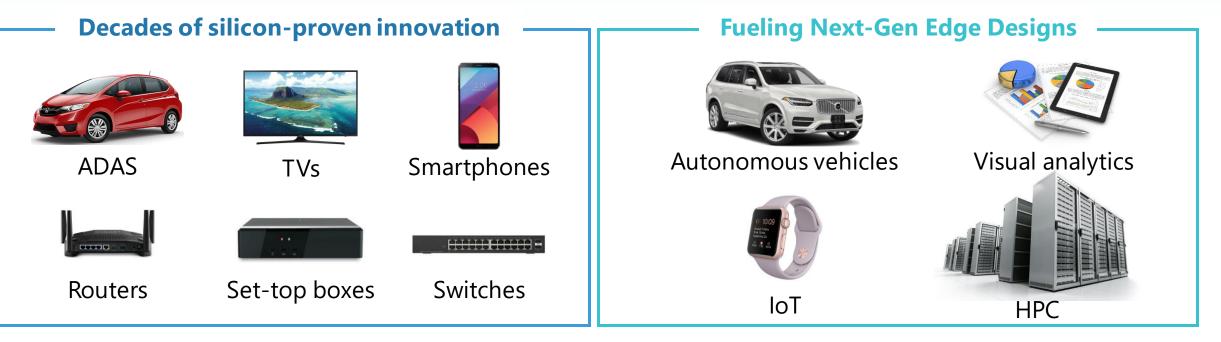

### Wave + MIPS: A Powerful History of Innovation

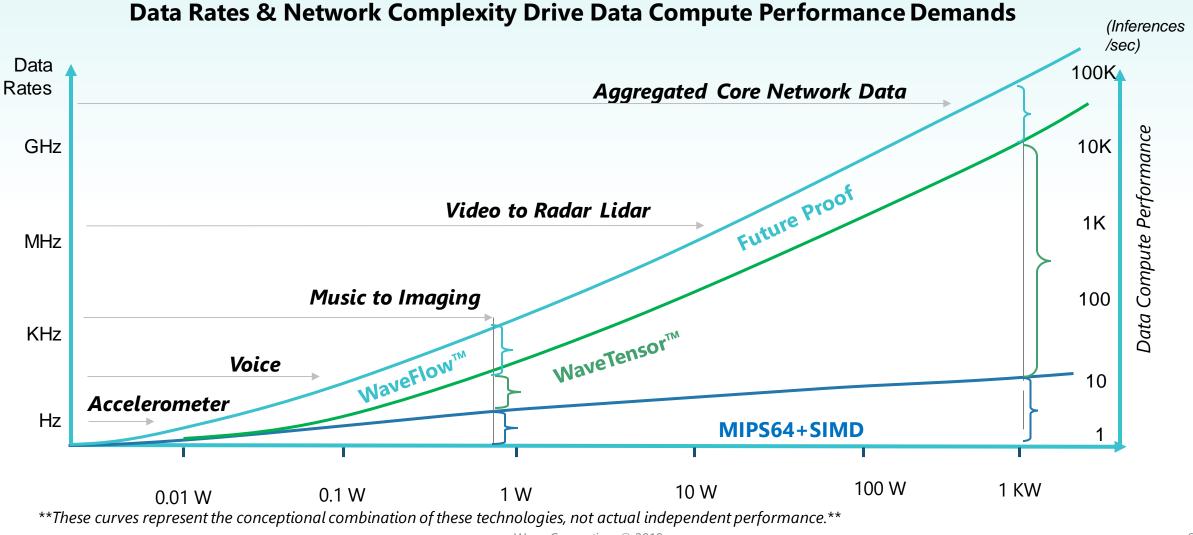

### What is Driving AI to the Edge?

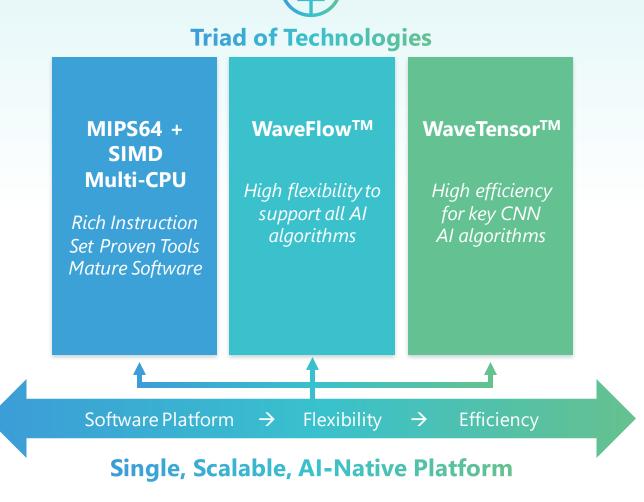

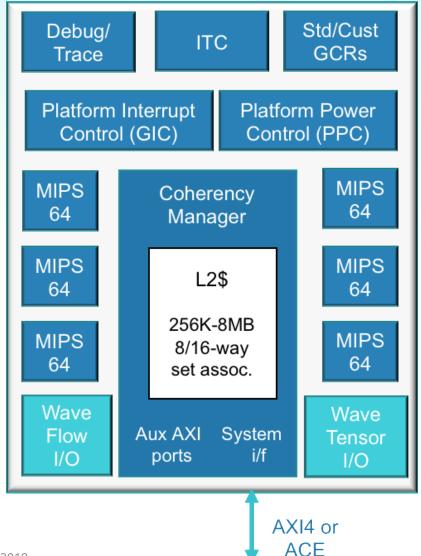

#### Scalable AI Platform: TritonAI<sup>™</sup> 64

#### **Key Benefits:**

- Highly Scalable to address broad AI use cases

- Supports Inference and Training

- High flexibility to support all AI algorithms

- High efficiency for key AI CNN algorithms

- Configurable to support AI use cases

- Mature Software Platform support

#### VAVE PUTING

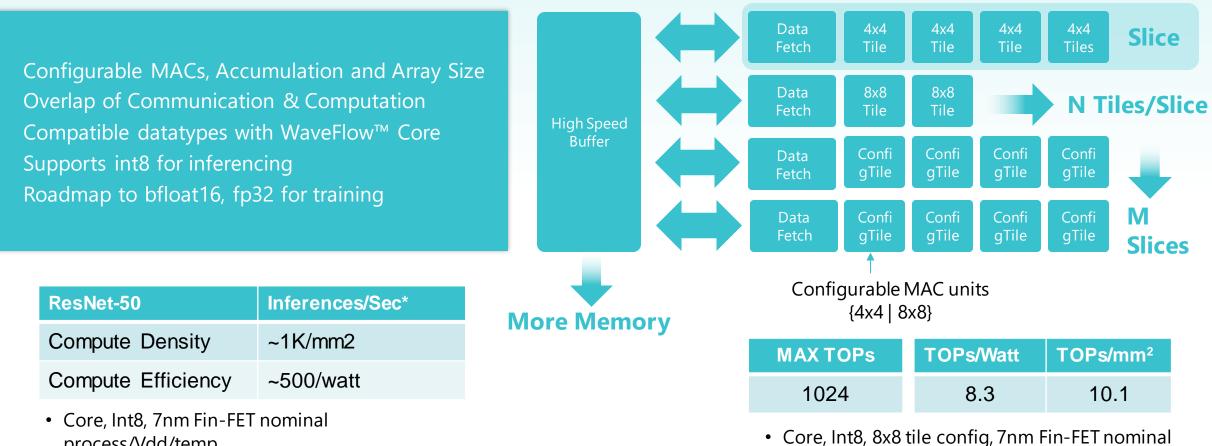

### WaveTensor <sup>™</sup> Configurable Architecture

process/Vdd/temp

#### Configurable Architecture for Tensor Processing

- process/Vdd/temp

- Batch=1, std model w/o pruning, performance and power vary with array size/configuration

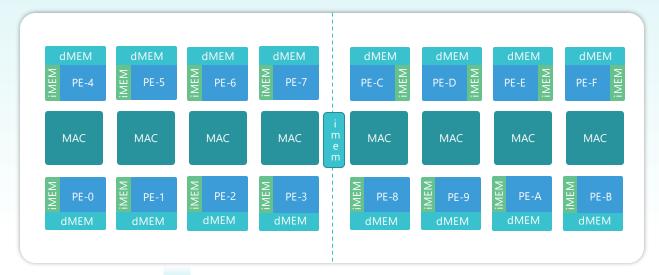

### WaveFlow<sup>™</sup> Reconfigurable Architecture

- Configurable IMEM and DMEM Sizes

- Overlap of communication & Computation

- Compatible datatypes with WaveTensor™

- Integer (Int8, Int16, Int32) for inference

- Roadmap (bfloat16, fp32) for training

Tile = (16 PE's + 8 MACS)

WaveFlow<sup>™</sup> = Wave Dataflow Array of Tiles

- Wide range of scalable solutions (2-1K tiles)

- Future Proof all AI algorithms

- Flexible 2 dimensional tiling implementation

- Reconfigurable for dynamic networks

- Concurrent Network execution

- Supports signal and vision processing

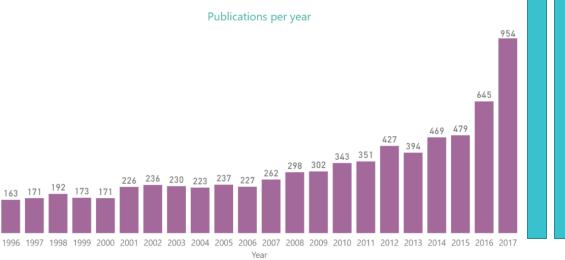

Looks like NIPS 2018 may have sold out in under 15 minutes. For those debating ML hype, getting a ticket to a ML conference is now more challenging than a Taylor Swift conference or a Hamilton showing

Follow

8:22 AM - 4 Sep 2018 from Iceland

What is the likelihood that your DNN accelerator will run all these "yet to be invented" networks?

Wave's TritonAI<sup>™</sup> 64 platform combines a reconfigurable processor with an efficient neural network accelerator.

Offers customers peace of mind and investment protection

### **Future-proof your Silicon**

#### **CNN Layers**

- Sparse Matrix-Vector Processing

- Stochastic pooling

- Median pooling (illumination estimation & color correction)

#### **Activation functions**

- Leaky rectified linear unit (Leaky ReLU) (used in Yolo3)

- Parametric rectified linear unit (PReLU)

- Randomized leaky rectified linear unit (RReLU)

#### **Custom Operators (e.g.)**

- Novel Loss Function

- New Softmax Implementation

- Image resize nearest neighbor

#### **Data Preprocessing**

- Scaling

- Aspect Ratio adjustment

- Normalizing

#### **Other Functions**

- Compression/Decompression

- Encryption/Decryption

- Sorting

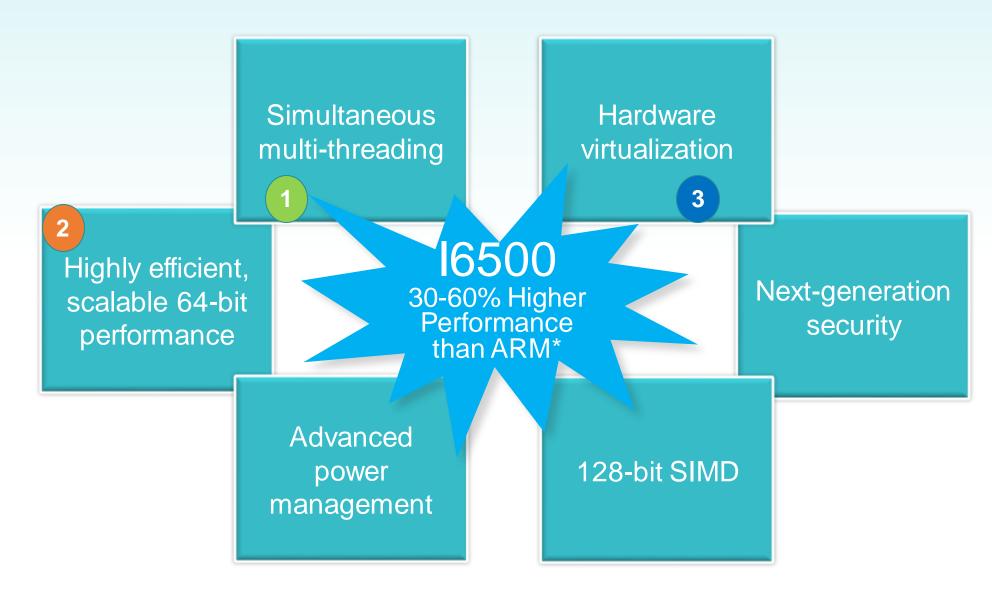

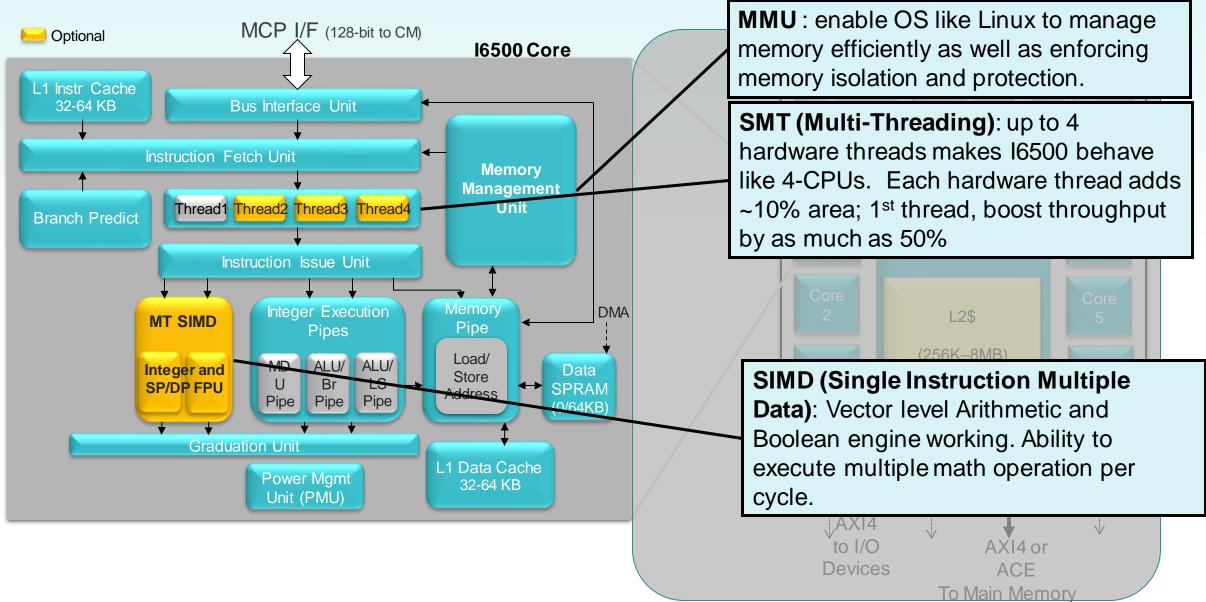

#### **MIPS-64** Processor

#### <u>MIPS-64</u>:

#### • MIPS64r6 ISA

- 128-bit SIMD/FPU for int/SP/DP ops

- Virtualization extensions

- Superscalar 9-stage pipeline w/SMT

- Caches (32KB-64KB), DSPRAM (0-64KB)

- Advanced branch predict and MMU

#### **Multi-Processor Cluster:**

- 1-6 cores

- Integrated L2 cache (0-8MB, opt ECC)

- Power mgmt. (F/V gating, per CPU)

- Interrupt control with virtualization

- 256b native AXI4 or ACE interface

#

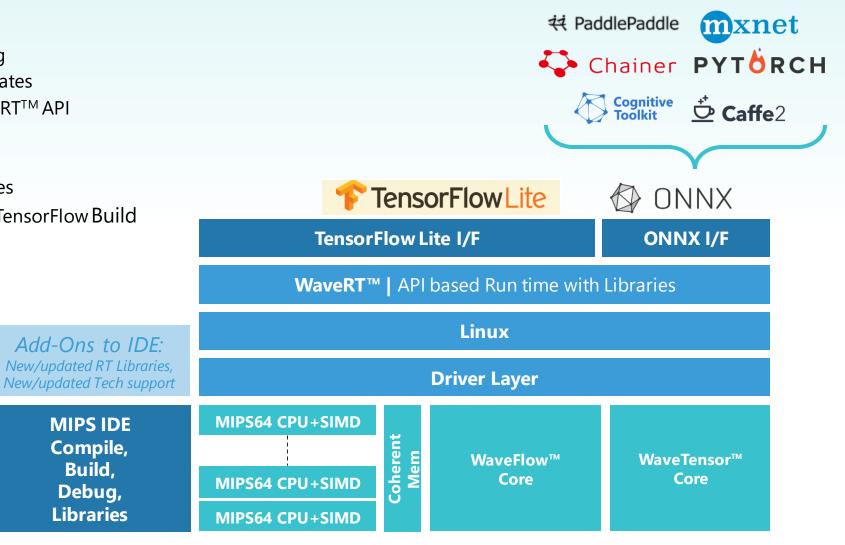

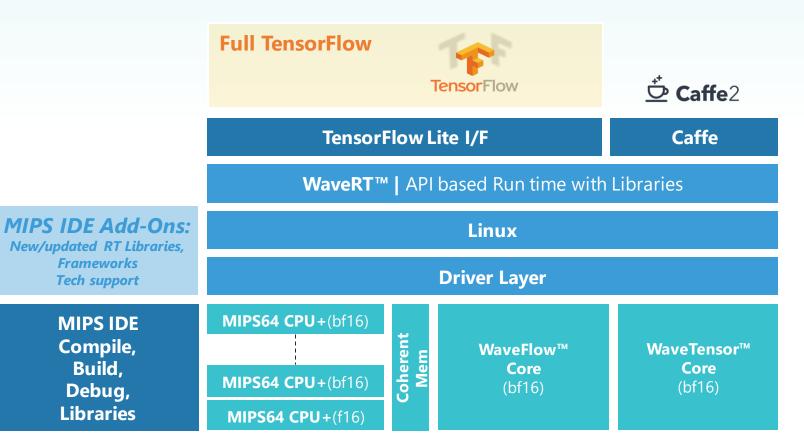

### Wave's TritonAI<sup>™</sup> 64 IP Software Platform

#### Software Platform:

- Mature IDE & Tools

- Driver Layer for Technology Mapping

- Linux Operating system support/updates

- Abstract AI Framework calls via WaveRT<sup>™</sup> API

- **Optimized AI Libraries for:** •

- CPU/SIMD/WaveFlow/WaveTensor

- TensorFlow-Lite Build support/updates

- Extensible to Edge Training with Full TensorFlow Build

#### **Configurable Hardware Platform:**

- MIPS64r6 ISA Cluster

- 1-6 cores

- 1-4 threads/core

- L1 I/D (32KB-64KB)

- Unified L2 (256K to 8 Mbytes)

- WaveFlow Tile Array

- 4 N Tiles

- WaveTensor Slice Array

- 1 N Slices

**MIPS IDE**

Compile,

Build.

Debug,

Libraries

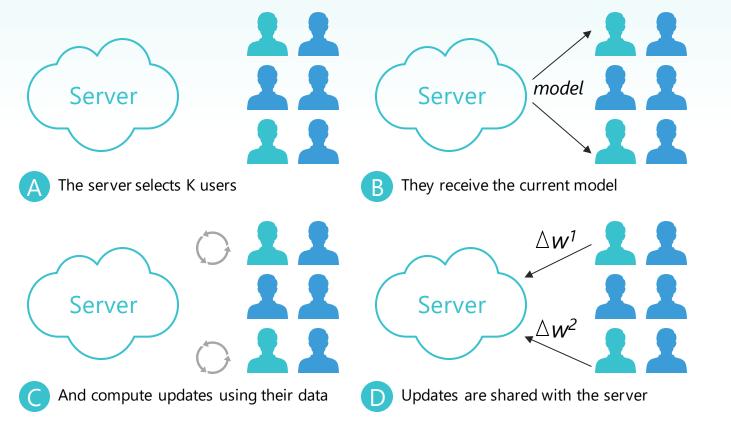

Federated Learning: The Next Frontier in Edge Al

### Better ML comes at a cost of collecting data Most training done in the cloud. i.e. Send your data to the cloud.

### **Diminished Privacy**

- Where is your data?

- Who has access to your data?

Incompatible with Banks, Insurance, Military, Health sectors

### Latency Problems

• Most access technologies are asymmetric

High Communications Costs

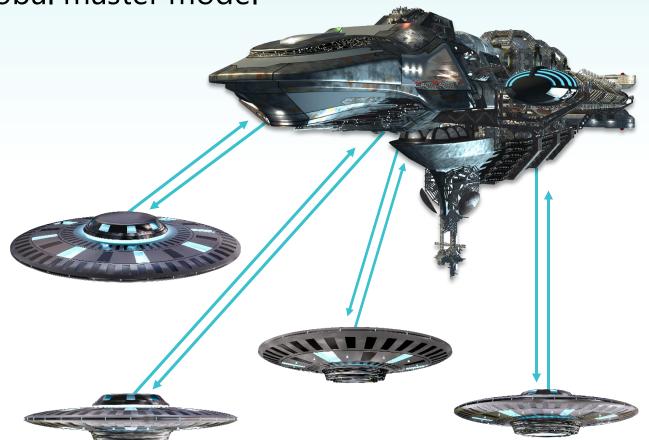

Federated learning uses training at the edge to refine the global model

- 1. Server selects a group of users

- 2. Users receive copy of central model

- 3. Users update model based on local data ("Training at the Edge")

- 4. Updates are shared with the server (User data remains private)

- 5. Server aggregates the changes and updates the central model

##

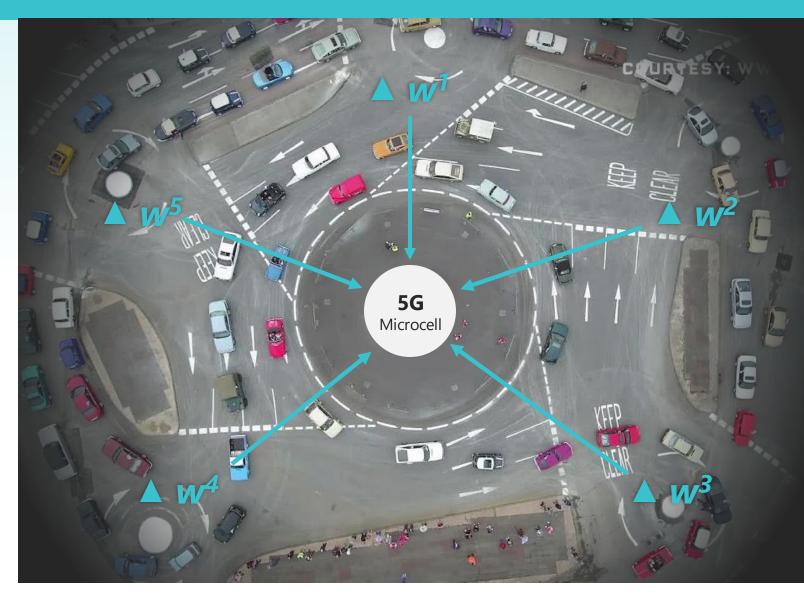

#### Federated Learning: Edge AI with Data Privacy

### **Benefits & Use Cases:**

- Transfer learning using local data at edge

- Edge data remains private

- Social networking applications

- Intelligent transportation systems that help increase passenger & pedestrian safety + traffic flow

Federated learning uses training at the edge to refine a global master model

#### **Benefits & Use Cases:**

- Transfer learning using local data at edge

- Edge data remains private

- Social networking applications

- Intelligent transportation systems that help increase passenger & pedestrian safety + traffic flow

### Edge Training Development

- Training Stacks for

- Federated Learning at the Edge

- Transfer Learning at the edge

- Local or personalized models

- Full TensorFlow Build

- WaveRT API Ext for Training

- Optimized SIMD FP32 & bfloat16 eigen libraries

- Deploy training at the edge

#### Wave's TritonAI<sup>™</sup> Platform Drives Inferencing to the Edge

Wave's TritonAI<sup>™</sup> Platform is a configurable, scalable & programmable offering customers' efficiency, flexibility and AI investment protection

Wave will enable "Training at the edge" with next-gen MIPS AI processor bfloat16 architectures

Thank You

# If you have questions or would like more information, visit <u>www.wavecomp.ai</u>

@wavecomputing

https://www.linkedin.com/company/wave-computing

https://www.facebook.com/WaveComp/

### **MIPS-Classic Cores**

Presented by Yuri Panchul MIPS Open Technical Lead MIPS Open Meetup in Moscow April 15, 2019

### **MIPS IP Cores - Features Summary**

|                        | microAptiv                     | M51xx        | M62xx        | interAptiv    | I7200                                  | 16500/-F                            | P5600           | P6600           |

|------------------------|--------------------------------|--------------|--------------|---------------|----------------------------------------|-------------------------------------|-----------------|-----------------|

| MIPS Primary ISA       | MIPS32 r5                      | MIPS32 r5    | MIPS32 r6    | MIPS32 r5     | nanoMIPS32                             | MIPS64 r6                           | MIPS32 r5       | MIPS64 r6       |

| Virtual/Phys Addr Bits | 32/32                          | 32/32        | 32/32        | 32/32         | 32/32                                  | 48/48                               | 32/40           | 48/40           |

| FPU                    | $\checkmark$ (UC version only) | $\checkmark$ | -            | MT            | -                                      | MT w/SIMD                           | Hi Perf w/SIMD  | Hi Perf w/SIMD  |

| DSP/SIMD extensions    | DSPASE r2                      | DSPASE r2    | DSPASE r2    | DSPASE r2     | DSPASE r2                              | MSA 128-bit                         | MSA 128-bit     | MSA 128-bit     |

| Virtualization         | -                              | $\checkmark$ | -            | -             | -                                      | $\checkmark$                        | $\checkmark$    | $\checkmark$    |

| Small code size ISA    | microMIPS32                    | microMIPS32  | microMIPS32  | MIPS16e2 ASE  | nanoMIPS32                             | -                                   | -               | -               |

| Multi-threading        | -                              | -            | -            | 2 VPE, 9 TC   | 3 VPE, 9 TC                            | 4 VPE                               | -               | -               |

| SuperScalar            | -                              | -            | -            | -             | Dual-issue in order                    | Dual-issue in order                 | Multi-issue OoO | Multi-issue OoO |

| Pipeline stages        | 5                              | 5            | 6            | 9             | 9                                      | 9                                   | 16              | 16              |

| Relative Frequency*    | 0.6x                           | 0.6x         | 0.75x        | 1x            | 0.95x                                  | 0.90x                               | 1.10x           | 1.10x           |

| SPRAMs (I/D/U)         | ✓ / ✓ / -                      | √ / √ / -    | ✓ / ✓ / -    | √ / √ / -     | $\checkmark / \checkmark / \checkmark$ | - / ✓ / -                           | - / - / -       | - / - / -       |

| L1 caches              | $\checkmark$                   | $\checkmark$ | $\checkmark$ | $\checkmark$  | $\checkmark$                           | $\checkmark$                        | $\checkmark$    | $\checkmark$    |

| L2 cache               | -                              | -            |              | $\checkmark$  | $\checkmark$                           | $\checkmark$                        | $\checkmark$    | $\checkmark$    |

| Coherent Multi-Core    | -                              | -            | -            | Up to 4 cores | Up to 4 cores                          | Up to 6 cores,<br>Up to 64 clusters | Up to 6 cores   | Up to 6 cores   |

| Native System Bus I/F  | AHB-Lite                       | AHB-Lite     | AXI          | OCP 2 or AXI  | AXI                                    | AXI or ACE                          | AXI             | AXI             |

\* Relative Frequencies are approximate, are provided for rough guidance only, and will vary to some extent in different process nodes

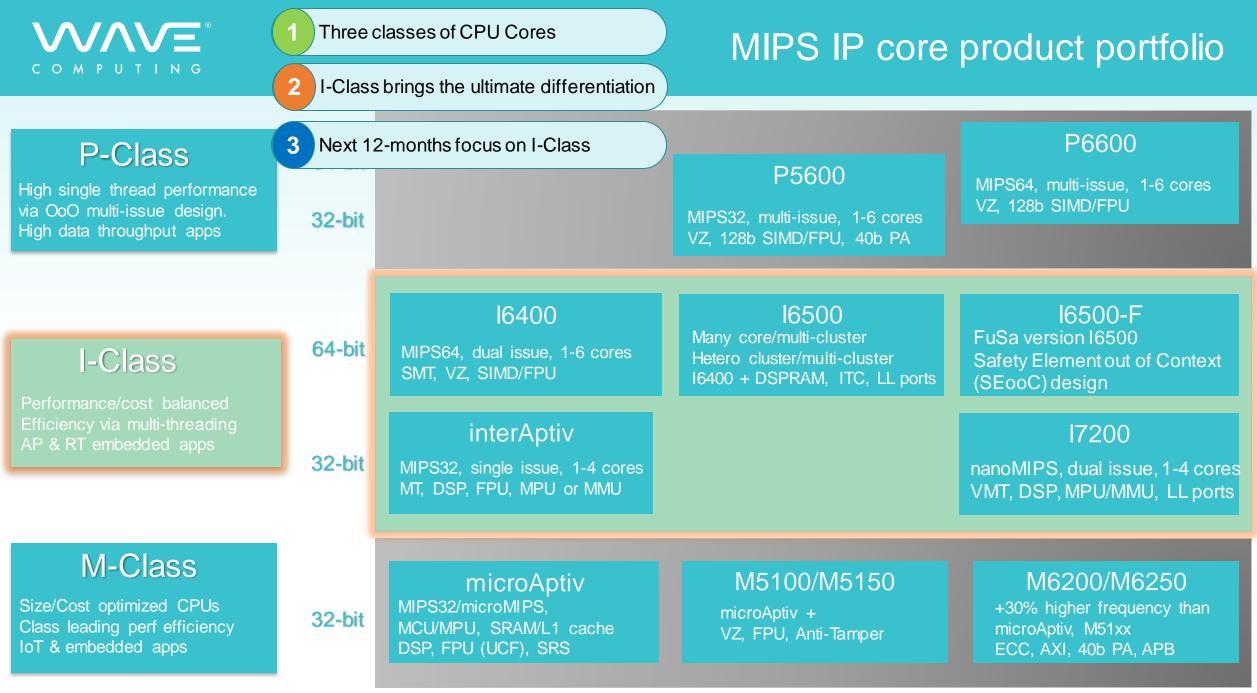

### **MIPS** technology differentiation

MIPS architecture and IP cores offer powerful, unique capabilities

#### **MIPS IP cores**

- 1. Offer leading Power Performance Area (PPA) across the range

- 2. Provide ultimate scalability: multi-thread, multi-core, multi-cluster

- 3. Address Functional Safety to ISO 26262 for automotive and IEC 61508 for industrial

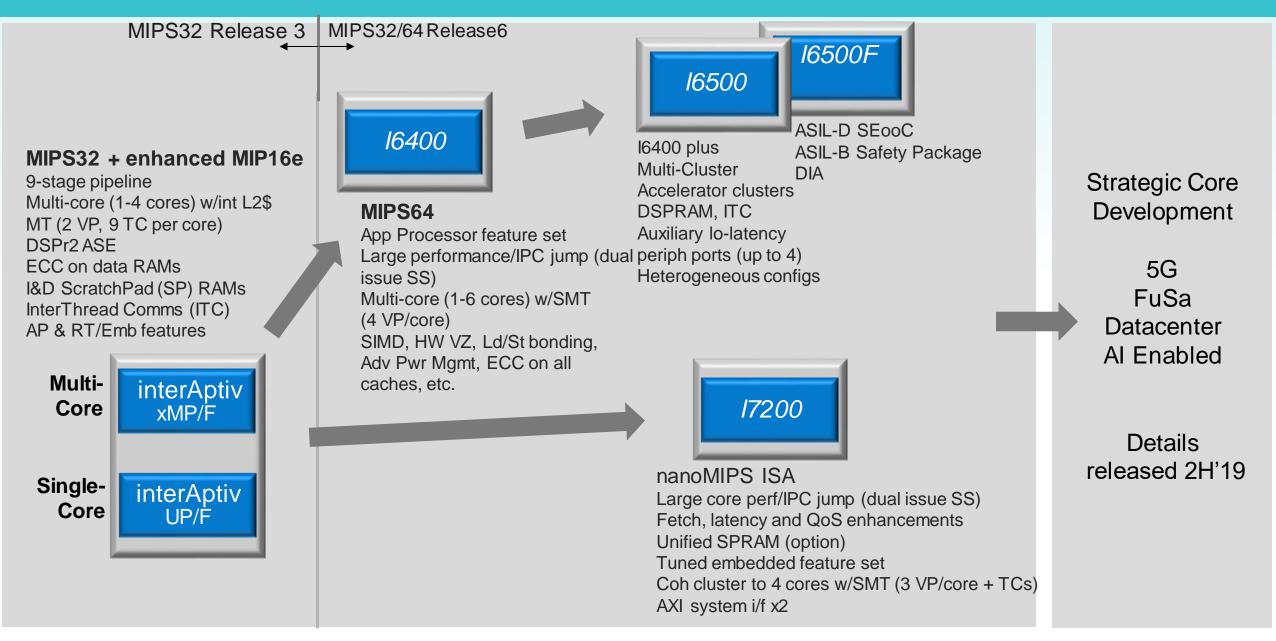

#### **MIPS® I-Class Processor Core Roadmap**

#### MIPS32 and MIPS64 evolution

Setting a new standards in mainstream 64-bit processing

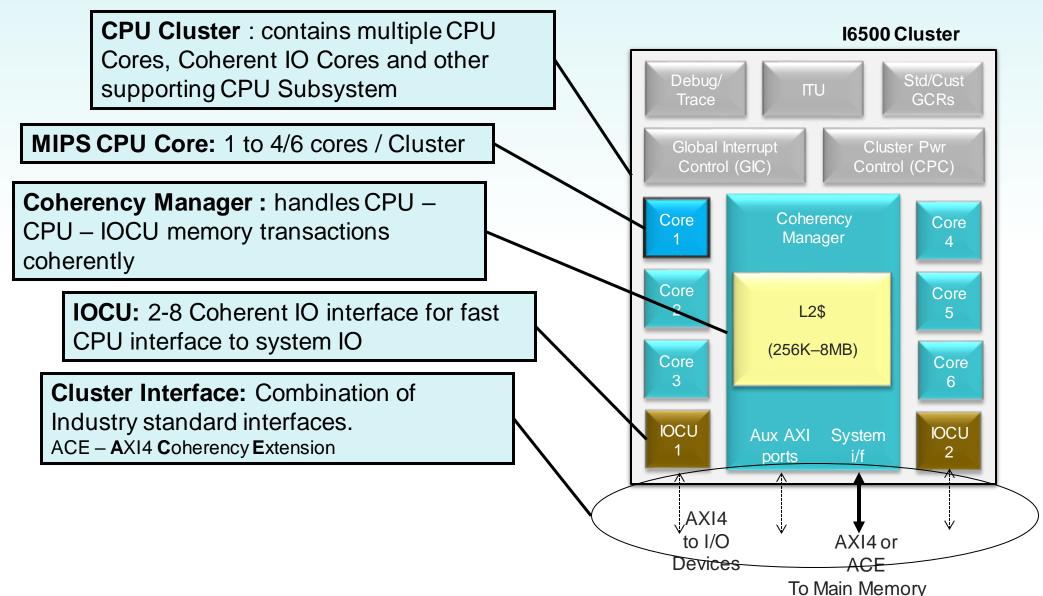

### Key Components of a Multi-Core Cluster?

#### How to build a Multi-Core Cluster?

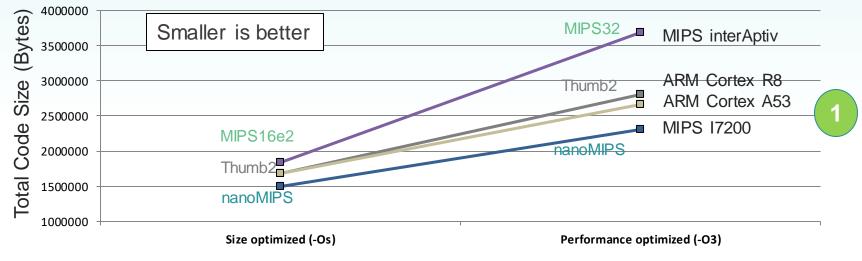

16500

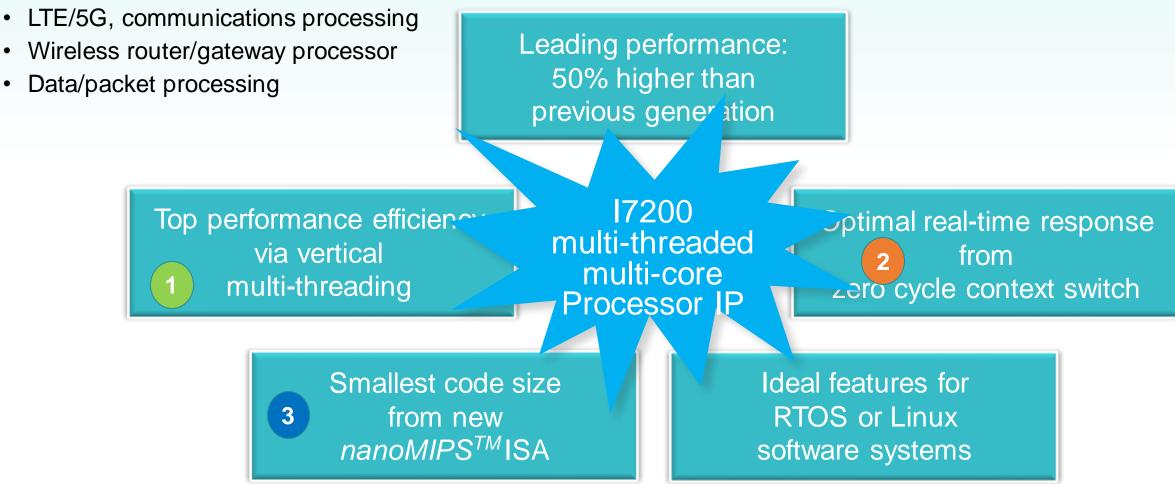

- Multi-threaded multi-core 32-bit processor IP

- Designed for high performance embedded systems with real-time requirements

3

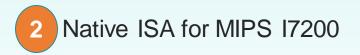

#### nanoMIPS ISA – advancing small code size

Achieves outstanding code density targeting small footprint applications or constraint devices

gcc compiler, with indicated optimization target

**Success Stories**

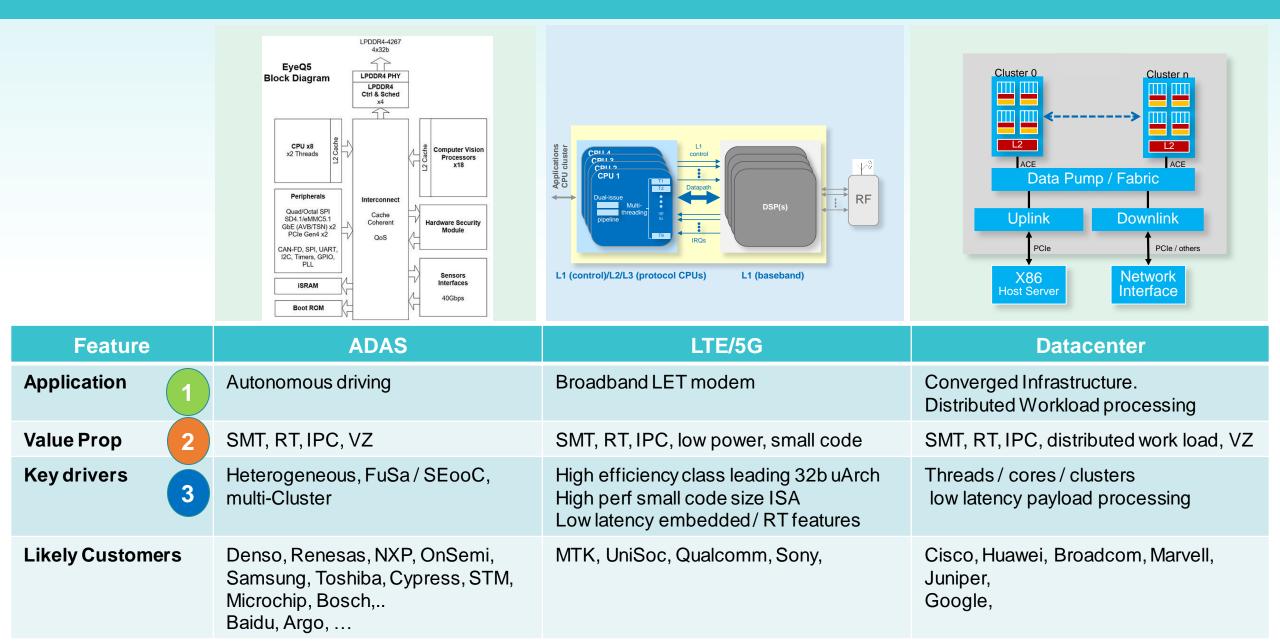

Market specific use-cases

#### **Classical Application Segments**

### Application Segment 1 ADAS

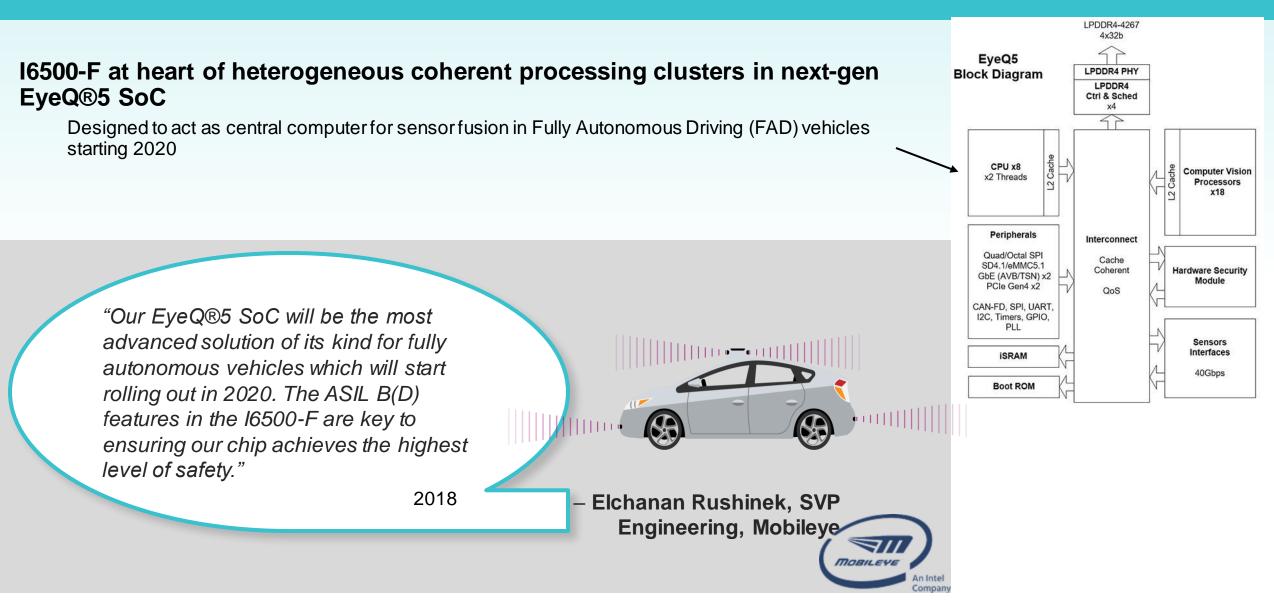

### **I6500-F lead customer: Mobileye ADAS Platform**

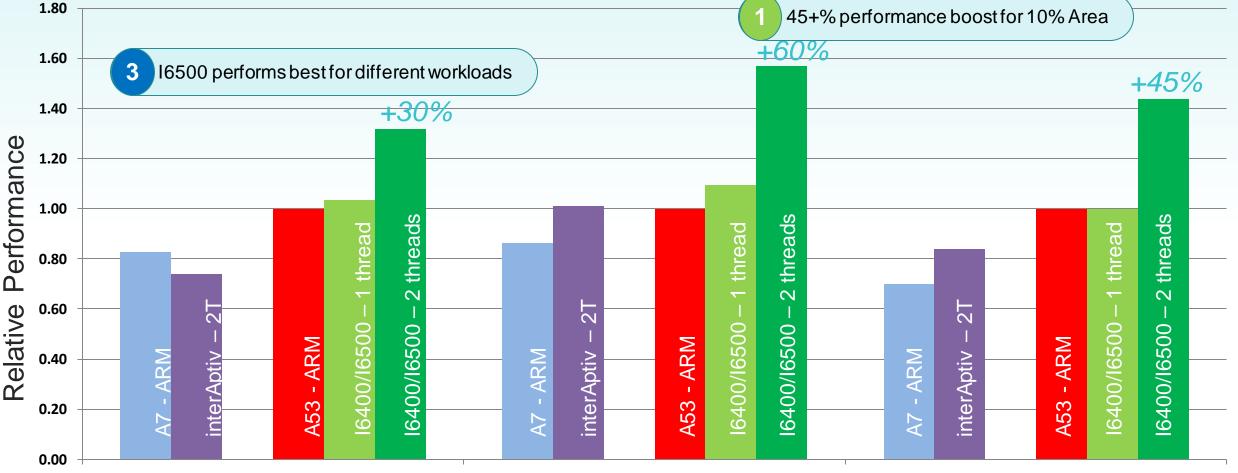

Per core, normalized to A53 Values (@ same frequency)

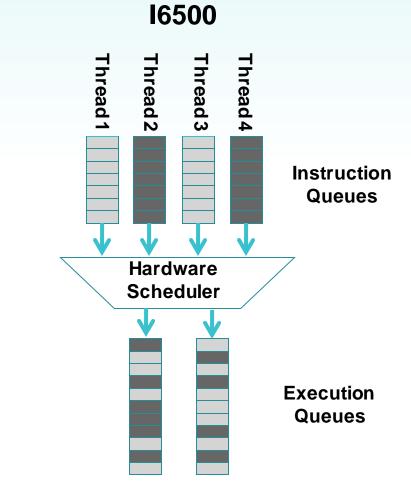

### Simultaneous Multi-Threading

DMIPS - 32b

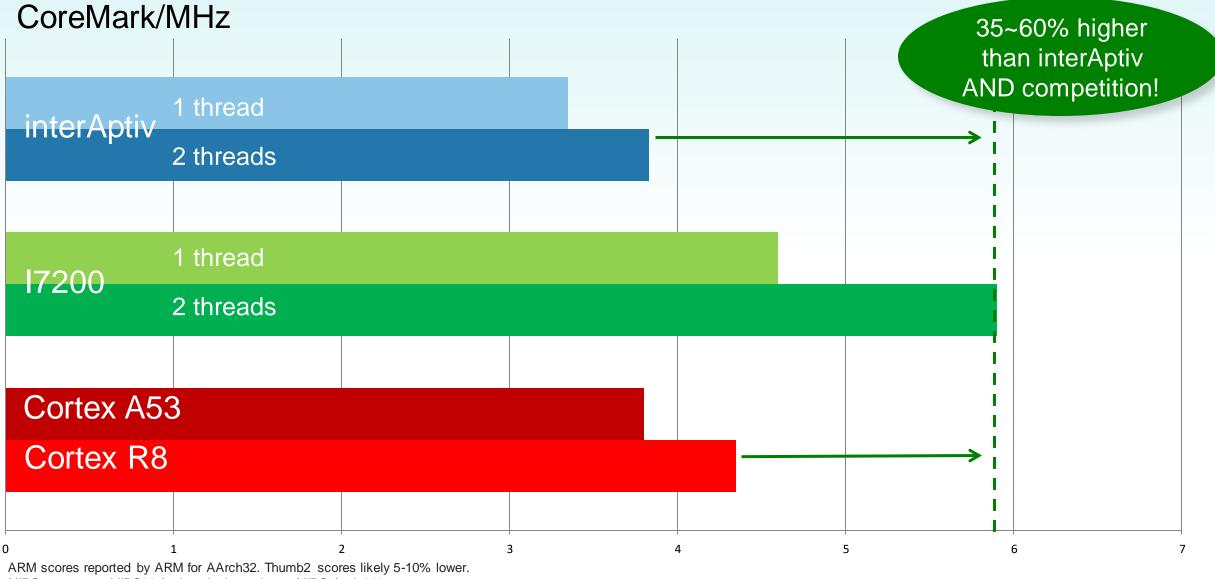

#### CoreMark

#### SPECint2000 (rate)

Based on Cortex A53 data reported by ARM on website and/or in presentation materials, plus benchmarked results on Linaro (HiSilicon Octa A53 Kirin620) with Linux kernel: 3.18.0-linaro-hikey SMP preempt, RFS Debian squeeze, with GCC-based 5.0.0 toolchain. A7 scores are ARM claims. Measured results are lower.

16400 results are based on production released RTL, FPGA platform benchmarking and in case of SPEC, 1 enhancement for next release performance models • testing

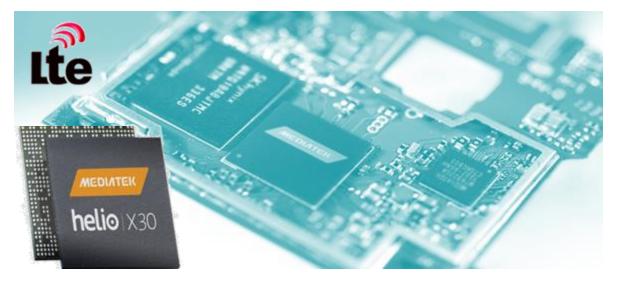

## Application Segment 2 LTE/5G

### Success Story, Multi-threading & Mediatek

### 17200

RF

|                   | Mediatek 5G LTE modem                                                                                                                                                                                                              | About MIPS in the application                                                                                    |

|-------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------|

| LTE               | <ul> <li>Mediatek designed MIPS into modem across multiple products</li> <li>First version, Helio X30, in production</li> </ul>                                                                                                    |                                                                                                                  |

| MIPS<br>Advantage | <ul> <li>Hardware Multi-Threading (MT)</li> <li>Fast inter-thread communications</li> <li>Higher performance/high processing efficiency</li> <li>Scalability         <ul> <li>1-4 cores, 2 threads per core</li> </ul> </li> </ul> | Stories CPU A<br>CPU 2<br>CPU 2<br>CPU 1<br>CPU 1<br>CPU 1<br>CPU 1<br>CPU 2<br>CPU 1<br>Dual-issue<br>threading |

|                   | Deterministic ; Real-time interrupts                                                                                                                                                                                               | L1 (control)/L2/L3 (protocol CPUs) L1 (baseband)                                                                 |

"MIPS CPUs, with their powerful multi-threading capability, offer a combination of efficiency and high throughput for LTE modems that contributes significantly to system performance." *said Dr. Kevin Jou, SVP and CTO, MediaTek*. 2018

### **I7200 Performance Advantage**

MIPS scores are MIPS32 for interAptiv, and nanoMIPS for I7200

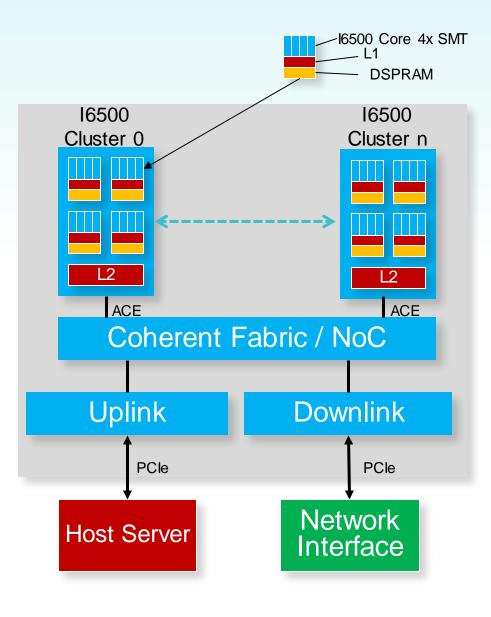

Application Segment 3 Data-center

Scala

3

- Scalable Multi-threading to Multi-core to Multi-cluster

- Configurable Heterogeneous inside & outside

- Optimized for High-throughput data processing applications

- Real-time, secure, deterministic and low latency

"The MIPS Simultaneous Multi-Threading architecture is an important technique to ensure that such workloads run efficiently as measured by the CPU's instructions per clock, or IPC. We have seen that this efficiency translates directly into a smaller area as well as lower power for silicon implementations based on MIPS." 2018

Pradeep Sindhu, CEO of Fungible

# VAVE

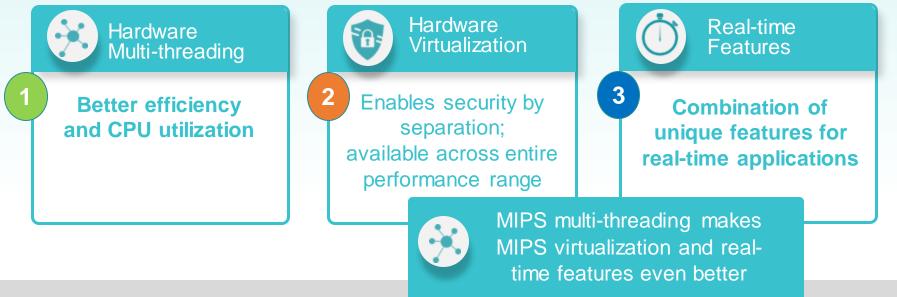

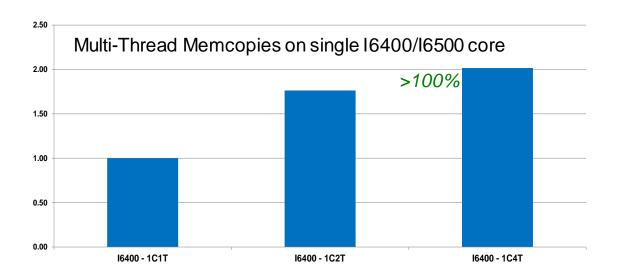

## 16400 & 6500 – Why Multi Threading?

A powerful differentiator among CPU IP cores

3

### Why MT?

- A path to higher performance, and higher efficiency

- 30%-60% higher performance for 10% per Thread increase

### Easy to use – programming model is same as multi-core

A thread looks like a core to standard SMP OS

### Simultaneous / concurrent execution

Zero Cycle overhead context switching

#

## MIPS IP Cores – Mapping to ARM

|                        | microAptiv                     | M51xx        | M62xx        | interAptiv              | <b>I7200</b>                           | 16500/-F                            | P5600           | P6600           |

|------------------------|--------------------------------|--------------|--------------|-------------------------|----------------------------------------|-------------------------------------|-----------------|-----------------|

| MIPS Primary ISA       | MIPS32 r5                      | MIPS32 r5    | MIPS32 r6    | MIPS32 r5               | nanoMIPS32                             | MIPS64 r6                           | MIPS32 r5       | MIPS64 r6       |

| Virtual/Phys Addr Bits | 32/32                          | 32/32        | 32/32        | 32/32                   | 32/32                                  | 48/48                               | 32/40           | 48/40           |

| FPU                    | $\checkmark$ (UC version only) | $\checkmark$ | -            | MT                      | -                                      | MT w/SIMD                           | Hi Perf w/SIMD  | Hi Perf w/SIMD  |

| DSP/SIMD extensions    | DSPASE r2                      | DSPASE r2    | DSPASE r2    | DSPASE r2               | DSPASE r2                              | MSA 128-bit                         | MSA 128-bit     | MSA 128-bit     |

| Virtualization         | -                              | $\checkmark$ | -            | -                       | -                                      | $\checkmark$                        | $\checkmark$    | $\checkmark$    |

| Small code size ISA    | microMIPS32                    | microMIPS32  | microMIPS32  | MIPS16e2 ASE            | nanoMIPS32                             | -                                   | -               | -               |

| Multi-threading        | -                              | -            | -            | 2 VPE, 9 TC             | 3 VPE, 9 TC                            | 4 VPE                               | -               | -               |

| SuperScalar            | -                              | -            | -            | -                       | Dual-issue in order                    | Dual-issue in order                 | Multi-issue OoO | Multi-issue OoO |

| Pipeline stages        | 5                              | 5            | 6            | 9                       | 9                                      | 9                                   | 16              | 16              |

| Relative Frequency*    | 0.6x                           | 0.6x         | 0.75x        | 1x                      | 0.95x                                  | 0.90x                               | 1.10x           | 1.10x           |

| SPRAMs (I/D/U)         | ✓ / ✓ / -                      | √ / √ / -    | ✓ / ✓ / -    | ✓ / ✓ / -               | $\checkmark   \checkmark   \checkmark$ | - / ✓ / -                           | - / - / -       | - / - / -       |

| L1 caches              | $\checkmark$                   | $\checkmark$ | $\checkmark$ | $\checkmark$            | $\checkmark$                           | $\checkmark$                        | $\checkmark$    | $\checkmark$    |

| L2 cache               | -                              | -            |              | $\checkmark$            | $\checkmark$                           | $\checkmark$                        | $\checkmark$    | $\checkmark$    |

| Coherent Multi-Core    | -                              | -            | -            | Up to 4 cores           | Up to 4 cores                          | Up to 6 cores,<br>Up to 64 clusters | Up to 6 cores   | Up to 6 cores   |

| Native System Bus I/F  | AHB-Lite                       | AHB-Lite     | AXI          | OCP 2 or AXI            | AXI                                    | AXI or ACE                          | AXI             | AXI             |

| Sample ARM<br>Mapping  | M3 I                           | M4           | M23 M33      | uting Confidential © 20 | R52 R7 R8                              | A53                                 | A57             | <b>A72</b>      |

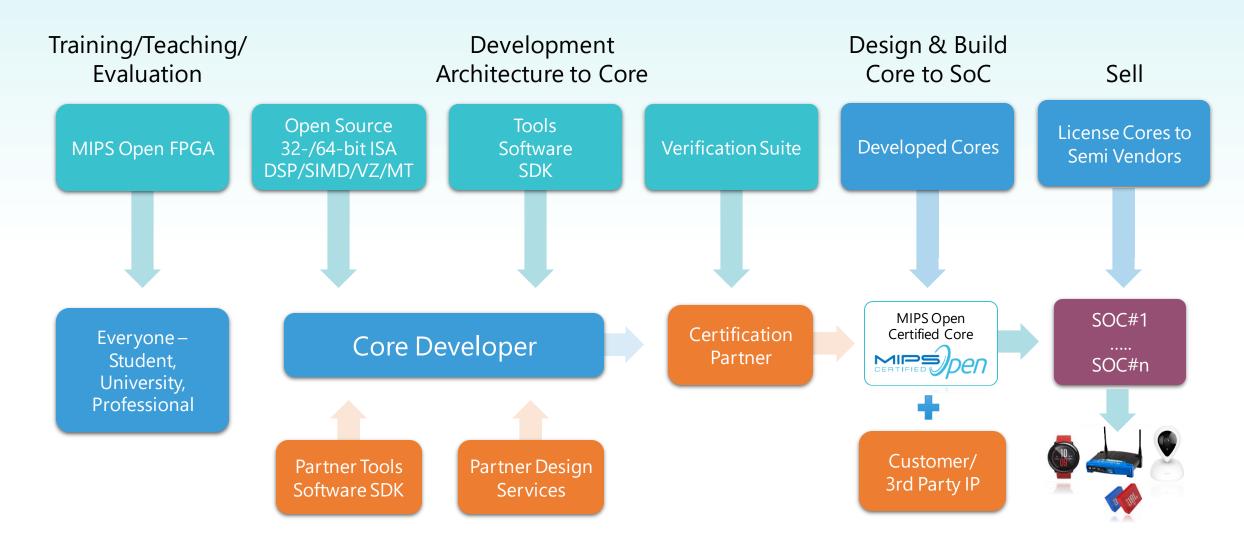

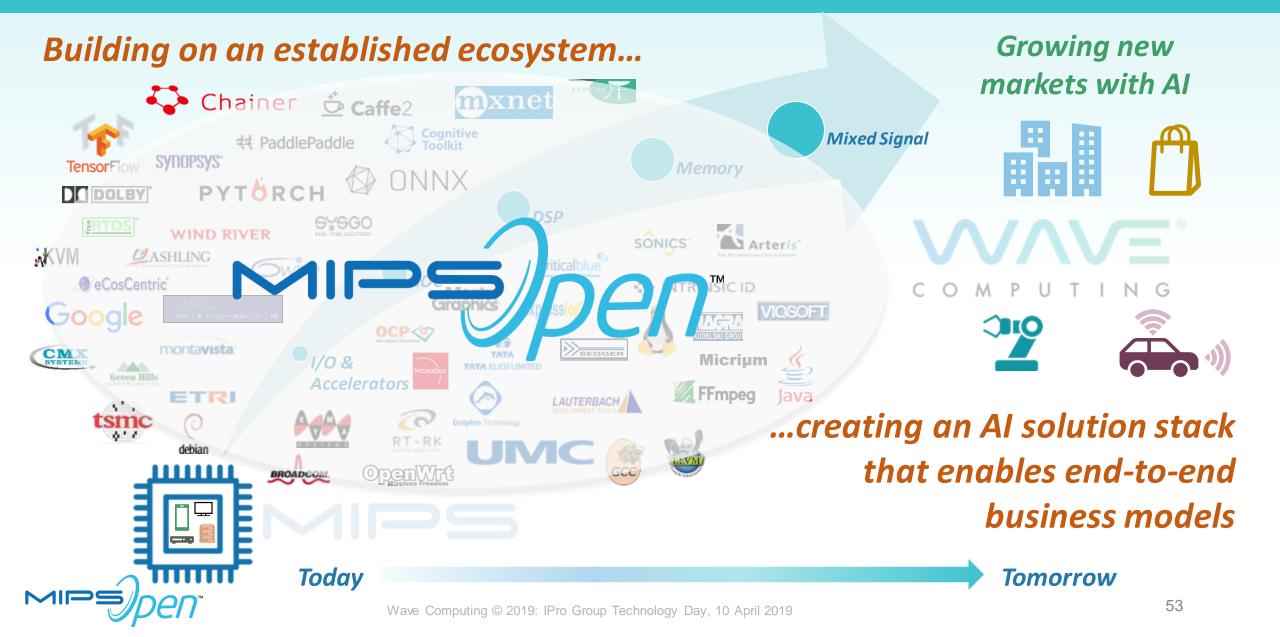

## **MIPS Open™** The New Standard in Open Use ISAs

Presented by Yuri Panchul, MIPS Open Technical Lead MIPS Open Meetup in Moscow, April 15, 2019

Wave Computing © 2019

| <b>mips</b><br>MIPS Computer<br>Systems Inc.<br>founded<br><b>1981</b>               |                                          | IF                                              | PS becomes<br>Plicensing<br>company             |                                   |                                   | Smar                                     | <mark>рилтек</mark><br>tphone<br>hodem |                                                           | Wave<br>Establishes MIPS<br>Open Advisory<br>Board                                    |

|--------------------------------------------------------------------------------------|------------------------------------------|-------------------------------------------------|-------------------------------------------------|-----------------------------------|-----------------------------------|------------------------------------------|----------------------------------------|-----------------------------------------------------------|---------------------------------------------------------------------------------------|

| 1980                                                                                 |                                          | 1990                                            |                                                 | 2000                              | 2                                 | 010                                      | 2017                                   | 2018                                                      | 2019                                                                                  |

| <b>1981</b> MIPS architecture<br>invented by<br>team from<br>StanfordImage: stanford | First MIPS<br>product ships:<br>R2000 uP | DTV/STB<br>product ships:<br><b>NEC</b><br>SONY | Cable Modem<br>product ships:<br><b>TOSHIBA</b> | Wi-Fi -<br>Residential<br>Gateway | <section-header></section-header> | Automo<br>MCUs<br>& ADAS<br>MICI<br>MICI | S<br>ROCHIP                            | Wave<br>Acquires<br>MIPS<br>Wave<br>Launches<br>MIPS Open | Joins AWS,<br>Facebook,<br>Google &<br>Samsung on UC<br>Berkeley's BAIR<br>initiative |

#

- Accelerates innovation for system-on-chip designs

- Expands adoption of MIPS RISC architecture & grows supporting ecosystem

- Dedicated Advisory Board prevents architectural fragmentation

- Delivers peace of mind & investment protection for existing MIPS customers

| Unified Approach                                                                                                             | Proven                                                                                                                                                                                                                                               | Established                                                                                                                                    | Matured                                                                                                                                    |

|------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------|

|                                                                                                                              | Architecture                                                                                                                                                                                                                                         | Ecosystem                                                                                                                                      | Technology                                                                                                                                 |

| <ul> <li>Compatibility</li> <li>No Fragmentation</li> <li>Same tools, software</li> <li>Flexibility – UDI support</li> </ul> | <ul> <li>MIPS architecture-<br/>based designs are shipping<br/>in billions of devices</li> <li>Shipping Products –<br/>wired modems, wireless<br/>modems – LTE/5G/Wi-Fi, IoT,<br/>automotive –<br/>ADAS, data centers,<br/>AI and others.</li> </ul> | <ul> <li>Well-established</li> <li>Tools, software,<br/>applications, boards</li> <li>Supported and used by<br/>customers/ partners</li> </ul> | <ul> <li>30+ years of legacy of<br/>MIPS architecture</li> <li>Enabler to build the next<br/>trillion devices/<br/>applications</li> </ul> |

MIPS Open is the World's First Commercial-ready, Silicon Proven, Feature-Rich Architecture Available for Open Use

## C O M P U T I N G

### MIPSOpen.com Now Live

DOWNLOADS MIPS OPEN<sup>TM</sup> COMPONENTS V RESOURCES V ABOUT V

## Wave's First MIPS Open Program Components Now Live

Immediate Access to the Proven, Industry-Standard and Patent-Protected MIPS RISC Architecture

# Stave Computing © 2019 – Confidential

## MIPS Open<sup>™</sup> Components

| MIPS Open ISA                                                                                                                                                                   | MIPS Open Tools                                                                                                                                                                                                               | MIPS Open FPGA                                                                                                                                                                                                                                                                                                                                                                              | MIPS Open Cores                                                                                                                                                       |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <ul> <li>Latest R6 version of 32-<br/>bit/64-bit ISA</li> <li>Extensions such as<br/>Virtualization, Multi-<br/>threading, SIMD, DSP and<br/>microMIPS architectures</li> </ul> | <ul> <li>IDE for Embedded RTOS<br/>and Linux Embedded<br/>Edition</li> <li>Enables MIPS software<br/>developers to build, debug,<br/>and deploy applications on<br/>MIPS-based hardware and<br/>software platforms</li> </ul> | <ul> <li>Getting Started Guide -<br/>provides MIPS Open<br/>FPGA system as a set of<br/>Verilog files</li> <li>Labs - includes 25 hands-on<br/>labs that guide users<br/>in exploring computer<br/>architecture &amp; system-level<br/>design</li> <li>SOC - shows how to build a<br/>system-on-chip design<br/>based on MIPS Open FPGA<br/>that loads the open source<br/>Linux</li> </ul> | <ul> <li>Low power, low footprint microAptiv cores</li> <li>Microprocessor(MPU)</li> <li>Microcontroller (MCU)</li> <li>Targeted for embedded applications</li> </ul> |

MIPS Open Components includes the latest MIPS R6 ISA, low power, low footprint microAptiv cores, microAptiv soft core targeted for FPGA and tools for software development.

| Open Use License                                                                                                                                                                                       | Certification                                                                                                                                                             | Patent License                                                                                                                                                                                  | Comprehensive<br>Package                                                                                                                           |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------|

| <ul> <li>MIPS Open use<br/>license includes:</li> <li>Latest MIPS R6<br/>architecture documents</li> <li>microAptiv cores</li> <li>Tools</li> <li>microAptiv softcore<br/>targeted for FPGA</li> </ul> | <ul> <li>Access to certification<br/>services to core<br/>developers</li> <li>Verification and<br/>Certification of cores<br/>developed using<br/>MIPS R6 ISA.</li> </ul> | <ul> <li>Right and license<br/>under R6 architecture<br/>patents to design,<br/>build and sell cores</li> <li>Use of the "MIPS<br/>Certified" trademark<br/>logo for certified cores</li> </ul> | <ul> <li>Complete package</li> <li>Instruction set,<br/>cores, tools for<br/>the community to<br/>accelerate innovation at<br/>the edge</li> </ul> |

MIPS Open provides a comprehensive open use package and tools to enable fast time to market for certified cores.

#

## Evolving the MIPS Ecosystem for AI at the Edge

Individual Membership Entry level

FREE

- Allows participation in all working groups and access to all working group materials.

- Represent individual, academic and non profits interests.

#### Silver Membership Entry level of corporate membership.

\$ 10,000

per year

- Allows participation in all working groups and access to all working group materials.

- Right to vote on working group initiatives.

- Can be appointed to lead a working group. If so appointed, automatically become a member of the technical steering committee.

- Can be nominated to run for election to the board of directors as a Silver class representative.

- Vote as a Silver class for representation on the board of directors.

#### Gold Membership Middle tier of membership.

## \$ 50,000 per year

- Allows participation in all working groups and access to all working group materials.

- Right to vote on working group initiatives.

- Can be appointed to lead a working group. If so appointed, automatically become a member of the technical steering committee.

- Can be nominated to run for election to the board of directors as a Gold class representative.

- Vote as a Gold class for representation on the board of directors. Allows participation in all working groups and access to all working group materials.

#### Platinum Membership

Decision-making level of membership

## \$ 100,000 per year

- Leadership and decision-making level of membership.

- Automatically appointed to the board of directors and the technical steering committee.

- Set direction, approve budgets and projects, appoint working group leaders, create new working groups, and supervise foundation staff.

- Have access to all foundation meetings and materials.

- Allows participation in all working groups and access to all working group materials.

- Right to vote on working group initiatives.Leadership and decision-making level of membership.

**Thank You**

Wave Computing © 2019